World Class Verilog, SystemVerilog & OVM/UVM Training

# The OVM/UVM Factory & Factory Overrides How They Work - Why They Are Important

Clifford E. Cummings Sunburst Design, Inc. www.sunburst-design.com

### ABSTRACT

Factory patterns are not new to the software world, and OVM/UVM have incorporated the factory into its primary methodology. But what does the factory really do and why is it important?

This paper will explain fundamental details related to the OVM/UVM factory and explain how it works and how overrides facilitate simple modification to the testbench component and transaction structures on a test by test basis. This paper will further demonstrate that OVM/UVM environments can mostly ignore the factory but will explain why the factory should be used.

# **Table of Contents**

| 1.                                                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                                                                            |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 2.                                                                 | The Term "Factory"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                                                                            |

| 3.                                                                 | Transaction Types Terminology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                                                            |

| 4.                                                                 | Tests & Regression Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                                            |

| 5.                                                                 | Why is there an OVM/UVM Factory?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                                            |

| 6.                                                                 | Registering Components & Transactions With the Factory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8                                                                                                            |

| 7.                                                                 | Object Constructors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8                                                                                                            |

| 8.                                                                 | Factory Registering and Creating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                                                                                                            |

| 9.                                                                 | Build Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                                                                            |

| 10.                                                                | Factory - Keys to Understanding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9                                                                                                            |

| 11.<br>Co                                                          | Simple Demonstration Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                              |

| FAC<br>FAC<br>FAC<br>FAC<br>FAC<br>TES<br>13.<br>FAC<br>FAC<br>FAC | Testbench Classes Using a Factory<br>TORY-BASED TRANSACTION<br>CTORY-BASED SEQUENCE<br>TORY-BASED TEST1<br>CTORY-BASED ENVIORNMENT<br>CTORY-BASED AGENT<br>CTORY-BASED AGENT<br>CTORY-BASED SEQUENCER<br>CTORY-BASED DRIVER<br>BUGGING THE UVM STRUCTURE AND FACTORY CONTENTS<br>T1 SIMULATION OUTPUT - FACTORY VERSION<br>test2 With Modified Transaction<br>CTORY-BASED TRANS2 TRANSACTION<br>CTORY-BASED TEST2<br>CTORY-BASED PACKAGE - TEST2<br>TORY-BASED PACKAGE - TEST2<br>CTORY-BASED P | . 12<br>. 12<br>. 13<br>. 14<br>. 15<br>. 15<br>. 15<br>. 16<br>. 17<br>. 19<br>. 20<br>. 21<br>. 22<br>. 23 |

| 14.<br>MC<br>FAC<br>FAC<br>TES                                     | T2 SIMULATION AND FACTORY SUBSTITUTION<br>test3 With Modified Driver<br>DIFIED TB_DRIVER2<br>CTORY-BASED TEST3<br>CTORY-BASED PACKAGE - TEST3<br>T3 STRUCTURE AND FACTORY TYPES REPORTS<br>T3 SIMULATION AND FACTORY SUBSTITUTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 26<br>. 26<br>. 27<br>. 28<br>. 29                                                                         |

| No<br>No<br>No                                                     | Testbench Classes Without Using the Factory<br>N-FACTORY-BASED TRANSACTION<br>N-FACTORY-BASED SEQUENCE<br>N-FACTORY-BASED TEST1<br>N-FACTORY-BASED ENVIORNMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 32<br>. 32<br>. 33<br>. 34                                                                                 |

| SNU                                                                | G 2012 2 The OVM/UVM Factory & Factory Overri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ides                                                                                                         |

| No  | N-FACTORY-BASED AGENT                               | 4 |

|-----|-----------------------------------------------------|---|

| No  | N-FACTORY-BASED SEQUENCER                           | 5 |

|     | N-FACTORY-BASED DRIVER                              |   |

| TES | T1 SIMULATION OUTPUT - NON-FACTORY VERSION          | б |

| 16. | test2 With Modified Transaction                     | 7 |

| FAG | CTORY-BASED TRANS2 TRANSACTION                      | 7 |

|     | N-FACTORY-BASED TEST2                               |   |

|     | N-FACTORY-BASED SEQUENCE                            |   |

|     | CTORY-BASED PACKAGE - TEST2                         |   |

| TES | T2 SIMULATION - NON-FACTORY VERSION                 | 0 |

| 17. | test3 simulation - non-factory version              | 0 |

| 18. | Where Does The ::type_id::create Command Come From? | 1 |

| 19. | Factory Overrides - Debugging 4                     | 6 |

| 20. | Using the new() Constructor                         | 6 |

| 21. | Using the Factory                                   | 7 |

| 22. | Conclusions                                         | 7 |

| 23. | Acknowledgements                                    | 8 |

| 24. | References                                          | 8 |

| 25. | AUTHOR & CONTACT INFORMATION                        | 8 |

# **Table of Figures**

| Figure 1 - Simple Demonstration Example Block Diagram                        | 10 |

|------------------------------------------------------------------------------|----|

| Figure 2 - test1 structure printout using this.print (factory version)       | 17 |

| Figure 3 - test1 factory.print (factory version)                             | 18 |

| Figure 4 - test1 UVM simulation output (factory version)                     | 19 |

| Figure 5 - test2 structure printout using this.print (non-factory version)   | 23 |

| Figure 6 - test2 - set_type_override_by_type factory.print (factory version) | 24 |

| Figure 7 - test2 UVM simulation output (factory version)                     | 25 |

| Figure 8 - test3 structure printout using this.print (factory version)       | 29 |

| Figure 9 - test3 - set_type_override_by_type factory.print (factory version) | 30 |

| Figure 10 - test3 UVM simulation output (factory version)                    | 31 |

# **Table of Examples**

| Example 1 - Standard new() constructor for UVM components                  | 5  |

|----------------------------------------------------------------------------|----|

| Example 2 - Standard new() constructor for UVM transactions (data objects) | 6  |

| Example 3 - top.sv module used for all tests                               | 11 |

| Example 4 - tb_pkg1.sv package file                                        | 11 |

| Example 5 - trans.sv sequence_item (factory version)                       |    |

| Example 6 - trans_sequence.sv sequence (factory version)                   |    |

| Example 7 - test1.sv test (factory version)                                | 13 |

| Example 8 - env.sv environment (factory version)                           | 14 |

| Example 9 - tb_agent.sv agent (factory version)                            | 15 |

| Example 10 - tb_sequencer.sv sequencer (factory version)                   | 16 |

| Example 11 - tb_driver.sv driver (factory version)                         |    |

| Example 12 - Debug printing for structure and factory registration         | 17 |

| Example 13 - trans2.sv sequence_item (factory version)                     |    |

| Example 14 - test2.sv test (factory version)                               |    |

| Example 15 - tb_pkg2.sv package file                                       |    |

| Example 16 - tb_driver2.sv driver (factory version)                        |    |

| Example 17 - test3.sv test (factory version)                               |    |

| Example 18 - tb_pkg3.sv package file                                       |    |

| Example 19 - trans.sv sequence_item (non-factory version)                  |    |

| Example 20 - trans_sequence.sv sequence (non-factory version)              |    |

| Example 21 - test1.sv test (non-factory version)                           |    |

| Example 22 - env.sv environment (non-factory version)                      |    |

| Example 23 - tb_agent.sv agent (non-factory version)                       |    |

| Example 24 - tb_sequencer.sv sequencer (non-factory version)               |    |

| Example 25 - tb_driver.sv driver (non-factory version)                     |    |

| Example 26 - trans2.sv sequence_item (non-factory version)                 |    |

| Example 27 - test2.sv test (non-factory version)                           |    |

| Example 28 - trans_sequence2.sv sequence (non-factory version)             |    |

| Example 29 - tb_pkg2.sv package file                                       | 40 |

## 1. Introduction

From an OVM/UVM perspective, besides instantiating the Design Under Test (DUT) and the SystemVerilog interface that interacts with the DUT, the top module typically places the virtual interface wrapper into a uvm\_object configuration lookup table and executes the **run\_test()** command.

In the top module source code, the **run\_test()** command should not include the name of the test to be run, because including the test name would force an engineer to modify the top-level module source code to run a new test, or would require the verification engineer to maintain multiple top-level modules. The **run\_test()** method call should extract its test name from the command line switch: **+UVM\_TESTNAME=**<*testname*>

Every test component and transaction type should be registered with the factory, but technically only the test must be registered with the factory (described later). No other testbench component is required to be registered with the factory (but they should!)

## 2. The Term "Factory"

The term factory refers to the fact that the recommended OVM/UVM methodology dictates that engineers should never construct components and transactions directly using the **new()** class constructor, but should makes calls to a special look-up table to create the requested component and transaction types. The factory is that special look-up table.

When you call the factory to create the requested component or transaction type, the factory itself will create the object by calling the constructor that was defined for that object. The constructors are typically one of the two following templates:

For components, there is a tree-like hierarchy required to build the testbench structure, where each component builds all of the components that are one-level lower in the hierarchy, so each component names (and builds) its children, and passes a pointer to itself (the **this** pointer) to each child component, so they know where they are located in the hierarchy (who is the parent device for each constructed component). For components, the typical constructor is shown in Example 1.

```

function new (string name, uvm_component parent);

super.new(name, parent);

endfunction

```

#### Example 1 - Standard new() constructor for UVM components

For transactions (data objects), each object is a unit of data with multiple fields, and transactions do not have a parent. For transactions, the typical constructor is shown in Example 2.

```

function new (string name="class_name");

super.new(name);

endfunction

```

#### Example 2 - Standard new() constructor for UVM transactions (data objects)

Notice that components typically do not include a default name value, but transactions do. Since a parent builds each component, the parent will name each child component, so any name that you would have given to a component is going to be overridden; hence, there is no good reason to name the components in their user-defined constructor. There are multiple examples on different websites and in different tutorials that include the class name as a default name value, and that set the parent to a default value of **null**. This is a complete waste of time and usually causes confusion for engineers that find the examples and try to determine when to add default names and **null** and when to omit them. The component defaults are just confusing and should just be omitted.

Transactions are also typically named when constructed, but there are times when transaction handles are declared but not created. For this reason, it is recommended that the user-defined constructor *should* include a name that matches the name of the transaction class where the constructor is defined.

## 3. Transaction Types Terminology

Even though the UVM base classes include a built-in uvm\_transaction type, it is rarely used directly. In general, verification engineers should build transaction types from the uvm\_sequence\_item type, which is extended from the uvm\_transaction type, and which is easily executed by uvm\_sequence types on a uvm\_sequencer component.

The term transaction type will be used throughout this paper to represent **uvm\_sequence\_item** type items executed by one or more **uvm\_sequences**.

## 4. Tests & Regression Tests

In OVM/UVM, a uvm\_sequence is really a partial or complete test, while the uvm\_test is really a collection of one or more sequences that are started on a uvm\_sequencer and hence what we typically call a test can really be thought of as a single test executing a single sequence, or a group of sequences executed as separate tests within the top-level test.

It is probably easier to think of uvm\_sequences as tests and the top-level test as a regression suite of those tests. Only one test is allowed to run per simulation and that test is called by executing the run\_test() command with the +UVM\_TESTNAME=<*test\_name*> command line switch. It is not possible to execute multiple top-level tests, which is why the top-level test should be thought of as the regression suite, while the sequences should be thought of as the individual tests that are run by the top-level regression suite (top-level test).

## 5. Why is there an OVM/UVM Factory?

If it is technically not necessary to register any components (except the top-level test) or transaction types with the factory, why have a factory?

The recommended method in OVM/UVM for creating testbench components or transaction objects is to use the built-in method **::type\_id::create** command, whose fuctionality is more fully explained in section 18.

Using the ::type\_id::create command makes a call to the factory to extract the requested component or transaction type and then uses the new() constructor that is included in the class type to build a copy of the class-type object, all of which is done at run time. Whatever class type is stored in the factory look-up table at the requested type\_id location, is extracted and created. The factory makes it possible to allow a compatible type to be stored at the desired location and therefore a compatible substitute can be automatically requested when the ::type\_id::create command is executed.

The factory permits a top-level test to make a substitution for one of the component or transaction types in the factory at run-time, before building the entire testbench environment using factory overrides.

For example, it may be desirable to do testing with two different transactions types, trans1 and trans2, where trans2 is an extension of trans1, but includes additional randomized data members. Since the sequencer, driver and monitor are all classes that are parameterized to a specific transaction type, the test writer can simply substitute the trans2 type for the trans1 type in the factory at the start of the test. Using a typical scenario, when the test builds the environment, and the environment builds the agent, and the agent builds the trans1-parameterized sequencer, driver and monitor, the parameterized agent components will be parameterized with the transaction type stored in the factory at the trans1 location, which is now the compatible trans2 type. There was no need to keep two copies of the sequencer, driver and monitor. It is still possible to run the older tests that used the trans1 type and use the exact same testbench structure to run new tests using the trans2 type.

As a second example, we may want to use the same transaction type, but we would like the data to be sent to the DUT in a serial fashion instead of a parallel fashion. The serial version of the DUT could use the exact same testbench structure as long as the driver sends the transaction as serial data and the monitor samples output transactions as serial data. For this environment, the test could substitute a second version of the driver and monitor into the factory so that when those components are built, the serial versions of those devices will be constructed without requiring the entire testbench environment to be re-coded.

Any components or transactions constructed from calls to the factory will simply look-up the required type\_id and construct that object. Since the components and transactions must be compatible types, the factory ensures the polymorphic type-safety of the required components.

| SNUG 2012 |  |

|-----------|--|

| Rev 1.1   |  |

The factory provides a partial replacement for the "when-inheritance" that one might use with Aspect-Oriented languages, only with finer granularity (one can replace specific objects without replacing all objects of the same type) and without the need for the compiler to re-compile all of the classes that make-up the testbench. Aspect Oriented programming has a simpler syntax, but factory substitution is much more compile efficient.

## 6. Registering Components & Transactions With the Factory

Testbench components should be registered with the factory using the command: `uvm\_component\_utils(component\_name)

Testbench transactions should be registered with the factory using the command: `uvm\_object\_utils(transaction\_type)

As will be described later, UVM ports are never registered with the factory, and covergroups are also never registered with the factory. In general TLM fifos are also not registered with the factory.

Two other factory registration macros have been deprecated from UVM and should not be used: `uvm\_sequence\_utils() and `uvm\_sequence\_utils(). These macros had the unfortunate side effect of tying a particular sequencer to a particular sequencer\_item type and conversely tied a particular sequence\_item type to a particular sequencer type, which greatly reduced the flexibility that should have existed in using and swapping different testbench component types and transaction types.

Unfortunately there are a very large number of examples in circulation that use both of these deprecated `ovm\_sequence/sequencer\_utils() macros, including in the OVM User Guide[2].

## 7. Object Constructors

Class based constructors are the built-in or user-defined **new()** constructors.

Constructing is typically done by calling the **new()** constructor, but OVM/UVM components and **sequence\_items/sequences** should be constructed using the **create()** command.

Guideline: construct OVM/UVM components using the **create()** command. Guideline: construct OVM/UVM sequence\_item/sequences using the **create()** command. Guideline: construct OVM/UVM port types using the **new()** constructor. Guideline: construct covergroups using the **new()** constructor in the component **new()** functions. Technically, none of the testbench components has to be built using the **create()** command. All of the testbench components (except the top-level test) can be built using the **new()** constructor, but using the **new()** constructor to build any of the testbench components or transaction types should never be done.

Using the **new()** constructor hard-codes the exact object type to be built into the testbench component files and severely limits the flexibility that was designed into the OVM/UVM methodologies. Using the factory **create** command allows the top-level test to substitute a compatible type into the factory and it is that type that will be created and used at run-time.

By using the factory, the **create** command simply calls for a component of the named type to be created, but the top-level test has the option to substitute into the factory a compatible extended type for any registered component type or transaction type.

## 8. Factory Registering and Creating

Once a component is registered with the factory, the component can be created in the **build\_phase()** at run-time, during the simulation, without the need to re-compile the new component or transaction types.

The factory provides a simulation-efficient mechanism to provide substitute components or transaction types on a test-by-test basis.

When properly coded, all of the components have been compiled and registered with the factory and it is the top-level test that can make a last-minute substitution at the beginning of the **build\_phase()** to determine the actual component type that will be created when that component **type\_id** is requested from another component.

Similarly and again when properly coded, any compatible transaction type that has been compiled and registered with the factory can be substituted by the top-level test before the required transaction type is even requested.

## 9. Build Phase

The OVM build() and UVM build\_phase() builds the entire testbench environment top down, and the first component built is the selected test. The test is an ideal place to override any of the testbench component types in the factory before any other component is created.

## 10. Factory - Keys to Understanding

**build\_phase()** execution happens top-down, so the top-level tests (and other components) can change the transaction types and components by doing overrides.

9

| SNUG 2012 |  |

|-----------|--|

| Rev 1.1   |  |

The test first makes run-time substitutions (overrides) into the factory for all components and transactions that do not match the base testbench and transaction structure, then proceeds to build each of the testbench components top-down. Since substitutions for components and transactions happened in the top-level test before any::type\_id::create commands were called, the new components and transactions will be called and constructed out of the factory.

## **11. Simple Demonstration Model**

In this section and in section 12, a simple demonstration model will be coded using the factory and then without the factory. Each example will also be coded using two more tests. In the second test, a second version of the transaction (trans2) will be added. In the third test, a second version of the tb\_driver will also be added. We will examine the coding efforts to do the additional tests with the modified transaction and tb\_driver.

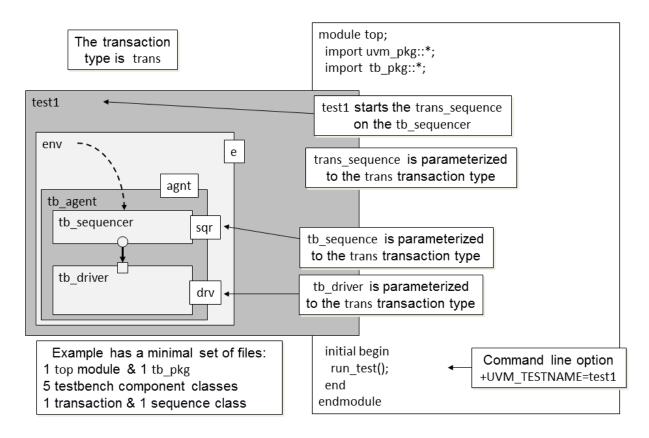

Figure 1 - Simple Demonstration Example Block Diagram

The simple demonstration model uses 1 top-module, 1 tb\_pkg, 5 component classes, 1 transaction class and 1 sequence class.

#### Common top module

For both the factory and non-factory versions of the tests, a common top-module will be used that, for simplicity purposes, will not contain a DUT to test. The top module simply uses the **run\_test()** command to start the simulations, and each simulation will specify the desired test using the +**UVM\_TESTNAME**=<*testname*> command line option. The common top-module is shown in Example 3.

```

module top;

import uvm_pkg::*;

import tb_pkg::*;

initial begin

run_test();

end

endmodule

```

Example 3 - top.sv module used for all tests

### 12. Testbench Classes Using a Factory

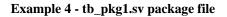

The classes in the test1-version of the factory-based example are included into the tb\_pkg shown in Example 4. It is important to include the classes in the correct order to ensure that classes that depend upon other class definitions, are included after the required classes are already included.

```

`ifndef TB_PKG

`define TB_PKG

`include "uvm_macros.svh"

package tb_pkg;

import uvm_pkg::*;

`include "trans.sv"

`include "tb_driver.sv"

`include "tb_sequencer.sv"

`include "tb_agent.sv"

`include "tb_agent.sv"

`include "trans_sequence.sv"

`include "trans_sequence.sv"

`include "test1.sv"

endpackage

```

`endif

#### Factory-based transaction

The transaction class is shown in Example 5, and includes two randomiazable data fields, the standard **new()** constructor and the recommended **convert2string()** method that can be called to show the current contents of the specified transaction object. The code that registers the transaction with the factory is the command, `uvm\_object\_utils(trans). A description of the behavior of the `uvm\_object\_utils() command will be explained in a later section of this paper.

```

class trans extends uvm_sequence_item;

`uvm_object_utils(trans)

rand bit [7:0] data;

rand bit [15:0] addr;

function new (string name="trans");

super.new(name);

endfunction

function string convert2string;

string s;

$sformat(s, "trans1: addr = %4h data = %2h", addr, data);

return s;

endfunction

endclass

```

Example 5 - trans.sv sequence\_item (factory version)

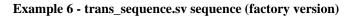

#### Factory-based sequence

The demonstration example also uses a simple sequence (shown in Example 6) that generates and randomizes 10 transactions that will be sent to the **tb\_sequencer**. The code that registers the transaction with the factory is the command, `uvm\_object\_utils(trans\_sequence).

```

class trans_sequence extends uvm_sequence #(trans);

`uvm_object_utils(trans_sequence)

function new (string name="trans_sequence");

super.new(name);

endfunction

task body();

trans tx = trans::type_id::create("tx");

repeat(10) begin

start_item(tx);

assert(tx.randomize());

finish_item(tx);

end

endtask

endclass

```

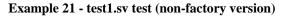

## Factory-based test1

The demonstration example is executed using the test1 class, as shown in Example 7.

The code that registers **test1** with the factory is the command,

```

`uvm_component_utils(test1). Although the transaction and sequence were both

registered with `uvm_object_utils(), the test is a testbench component, so it uses

`uvm_component_utils().

```

The test is the first component built after executing the **run\_test()** command in the **top** module. The test also references the factory to build the **env** and the command that accesses the **env** type from the factory is the command:

e = env::type\_id::create("e", this);

The ::type\_id::create() command will be contrasted to the new() constructor used in the non-factory version of this testbench.

```

class test1 extends uvm_test;

`uvm component utils(test1)

env e;

function new (string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build phase(phase);

e = env::type id::create("e", this);

endfunction

function void end_of_elaboration_phase(uvm_phase phase);

super.end_of_elaboration_phase(phase);

this.print();

factory.print();

endfunction

task run_phase(uvm_phase phase);

trans_sequence seq;

phase.raise_objection(this);

seq = trans_sequence::type_id::create("seq");

seq.start(e.agnt.sqr);

phase.drop_objection(this);

endtask

endclass

```

Example 7 - test1.sv test (factory version)

## Factory-based enviornment

The environment class for the demonstration example is shown in Example 8.

The code that registers the **env** with the factory is the command,

`uvm\_component\_utils(env). This will be the top-level environment that will be bulit by all of the tests in this example.

The test also references the factory to build the **tb\_agent** and the command that accesses the **tb\_agent** type from the factory is the command:

```

agnt = tb_agent::type_id::create("agnt", this);

class env extends uvm_env;

`uvm_component_utils(env)

tb_agent agnt;

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build_phase(phase);

agnt = tb_agent::type_id::create("agnt", this);

endfunction

endclass

```

Example 8 - env.sv environment (factory version)

## Factory-based agent

The agent class for the demonstration example is shown in Example 9.

The code that registers the tb\_agent with the factory is the command,

`uvm\_component\_utils(tb\_agent). This agent will build the sequencer-driver pair and frequently also builds a monitor. In this example, the monitor has been omitted to simplify the example.

The agent references the factory to build the **tb\_driver** and **tb\_sequencer**, using the commands:

```

tb_driver::type_id::create("drv", this);

drv =

sqr = tb_sequencer::type_id::create("sqr", this);

class tb agent extends uvm agent;

`uvm component utils(tb agent)

tb driver drv;

tb sequencer sqr;

function new(string name, uvm component parent);

super.new(name, parent);

endfunction

function void build phase(uvm phase phase);

super.build_phase(phase);

drv = tb_driver::type_id::create("drv", this);

sqr = tb sequencer::type id::create("sqr", this);

endfunction

function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

drv.seq_item_port.connect(sqr.seq_item_export);

endfunction

endclass

```

Example 9 - tb\_agent.sv agent (factory version)

## Factory-based sequencer

The sequencer class for the demonstration example is shown in Example 10.

The code that registers the tb\_sequencer with the factory is the command,

**`uvm\_component\_utils(tb\_sequencer).** Sequencers and drivers are classes that must be parameterized to the transaction type. The transaction type for this sequencer is **trans**, which is extended from the uvm\_**sequence\_item** type. UVM will check to make sure that the parameterized driver and sequencer are using compatible transaction types. When we change the transaction type for the demonstration example, we will again talk about what happens to the parameterized sequencer and driver.

Sequencers are typically pretty simple blocks of standard code and sequencers do not build any other sub-components.

```

class tb_sequencer extends uvm_sequencer #(trans);

`uvm_component_utils(tb_sequencer)

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

endclass

```

Example 10 - tb\_sequencer.sv sequencer (factory version)

### Factory-based driver

The driver class for the demonstration example is shown in Example 11.

The code that registers the tb\_driver with the factory is the command,

`uvm\_component\_utils(tb\_driver). As stated in the sequencer section, sequencers and drivers are classes that must be parameterized to the transaction type. The transaction type for this driver is trans, which is extended from the uvm\_sequence\_item type. UVM will check to make sure that the driver and sequencer are using compatible transaction parameters.

Drivers do not typically build any other sub-components.

```

class tb_driver extends uvm_driver #(trans);

`uvm component utils(tb driver)

function new (string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build_phase(phase);

endfunction

task run_phase(uvm_phase phase);

trans tx;

forever begin

seq_item_port.get_next_item(tx);

#10 `uvm info("tb driver", tx.convert2string(), UVM MEDIUM)

seq_item_port.item_done();

end

endtask

endclass

```

Example 11 - tb\_driver.sv driver (factory version)

### Debugging the UVM structure and factory contents

After assembling a rather complex UVM testbench environment, it is often useful to print out the structure of the testbench in tabular form and to query the types that were registered with the factory. A great technique to view the structural composition of the testbench classes and the factory setup is to call the this.print() and factory.print() methods in the end\_of\_elaboration\_phase() (as shown in Example 12) from the top-level testbench. By the time the end\_of\_elaboration\_phase() executes, the entire environment has already been built and connected, so these print() methods show what had been built in the testbench and the types that were registered with the factory.

```

function void end_of_elaboration_phase(uvm_phase phase);

super.end_of_elaboration_phase(phase);

this.print();

factory.print();

endfunction

```

Example 12 - Debug printing for structure and factory registration

The structural printout for test1 is shown in Figure 3. In this table, we can see the 5 testbench components: test1, env (e), tb\_agent (agnt), tb\_driver (drv) and tb\_sequencer (sqr).

UVM INFO /home/uvm/src/base/uvm root.svh(355) @ 0: reporter [NO DPI TSTNAME] UVM\_NO\_DPI defined--getting UVM\_TESTNAME directly, without DPI UVM\_INFO @ 0: reporter [RNTST] Running test test1... \_\_\_\_\_ Name Type Size Value \_\_\_\_\_ test1 @489 uvm\_test\_top env -t tb\_agent -rv tb\_driver -rsp\_port uvm\_analysis\_port -sqr\_pull\_port uvm\_seq\_item\_pull\_port -qr tb\_sequencer е @499 @508 aqnt drv @518 @535 @526 @544 sqr rsp\_export uvm\_analysis\_export seq\_item\_export uvm\_seq\_item\_pull\_imp \_ @552 \_ @658 arbitration\_queue array 0 lock\_queue array num\_last\_reqs integral 0 \_ 32 'd1 32 num\_last\_rsps 'd1 integral \_\_\_\_\_

Figure 2 - test1 structure printout using this.print (factory version)

The types registered in the factory for test1 are shown in Figure 3. In this list, we can see that there is currently no instance or type overrides in the factory, but the 5 testbench component

| SNUG 2012 |  |

|-----------|--|

| Rev 1.1   |  |

types: test1, env, tb\_agent, tb\_driver and tb\_sequencer, along with the transaction type (trans) and sequence type (trans\_sequence) have been registered with the factory.

## Factory Configuration (\*)

No instance or type overrides are registered with this factory

All types registered with the factory: 44 total

(types without type names will not be printed)

Type Name

------env

tb\_agent

tb\_driver

tb\_sequencer

test1

trans

trans\_sequence

(\*) Types with no associated type name will be printed as <unknown>

##

Figure 3 - test1 factory.print (factory version)

### test1 simulation output - factory version

When the **test1** test is executed, we see that indeed 10 **trans** transactions were executed as printed in the simulation output shown in Figure 4.

UVM\_INFO tb\_driver.sv(27) @ 10: uvm\_test\_top.e.agnt.drv [tb\_driver] trans1: addr = 74e9 data = 71 UVM\_INFO tb\_driver.sv(27) @ 20: uvm\_test\_top.e.agnt.drv [tb\_driver] trans1: addr = 15e4 data = c8 UVM\_INFO tb\_driver.sv(27) @ 30: uvm\_test\_top.e.agnt.drv [tb\_driver] trans1: addr = 0929 data = 05 UVM\_INFO tb\_driver.sv(27) @ 40: uvm\_test\_top.e.agnt.drv [tb\_driver] trans1: addr = 6a6a data = 56 UVM\_INFO tb\_driver.sv(27) @ 50: uvm\_test\_top.e.agnt.drv [tb\_driver] trans1: addr = 003e data = 33 UVM\_INFO tb\_driver.sv(27) @ 60: uvm\_test\_top.e.agnt.drv [tb\_driver] trans1: addr = 8249 data = e4 UVM\_INFO tb\_driver.sv(27) @ 70: uvm\_test\_top.e.agnt.drv [tb\_driver] trans1: addr = 4fe4 data = 7b UVM\_INFO tb\_driver.sv(27) @ 80: uvm\_test\_top.e.agnt.drv [tb\_driver] trans1: addr = 6e25 data = b6 UVM\_INFO tb\_driver.sv(27) @ 90: uvm\_test\_top.e.agnt.drv [tb\_driver] trans1: addr = 5a20 data = d6 UVM\_INFO tb\_driver.sv(27) @ 100: uvm\_test\_top.e.agnt.drv [tb\_driver] trans1: addr = 5a20 data = 2b UVM\_INFO tb\_driver.sv(27) @ 100: uvm\_test\_top.e.agnt.drv [tb\_driver] trans1: addr = 5a20 data = 2b UVM\_INFO /home/uvm/src/base/uvm\_objection.svh(1120) @ 100: reporter [TEST\_DONE] 'run' phase is ready to proceed to the 'extract' phase

--- UVM Report Summary ---

\*\* Report counts by severity UVM\_INFO: 13 UVM\_WARNING: 0 UVM\_ERROR: 0 UVM\_FATAL: 0 \*\* Report counts by id [NO\_DPI\_TSTNAME] 1 [RNTST] 1 [TEST\_DONE] 1 [tb\_driver] 10 \*\* Note: \$finish : /home/uvm/src/base/uvm\_root.svh(408) Time: 100 ns Iteration: 60 Instance: /top

#### Figure 4 - test1 UVM simulation output (factory version)

## 13. test2 With Modified Transaction

Now it is time to see what the factory can do to facilitate the creation of additional tests with minimal changes to the testbench structure and minimal modifications to the testbench source code.

## Factory-based trans2 transaction

For test2, we are going to use a modified transaction type called trans2. The only modifications to the trans2 type are the addition of a randomizable valid bit, and overriding the convert2string() method to report that this is a trans2 transaction and to add to the printout the contents of the valid bit. Using class extension, trans2 will be extended from trans, so the addr and data fields will be inherited from the original trans class. The trans2 code is shown in Example 13.

Just like the **trans** base class, the code that registers the transaction with the factory is the command, `uvm\_object\_utils(trans2).

```

class trans2 extends trans;

`uvm_object_utils(trans2)

rand bit valid;

function new (string name="trans2");

super.new(name);

endfunction

function string convert2string;

string s;

$sformat(s, "trans2: addr = %4h data = %2h valid=%b",addr,data,valid);

return s;

endfunction

endclass

```

Example 13 - trans2.sv sequence\_item (factory version)

### Factory-based test2

The code for the second test is shown in Example 14 and the code that registers test2 with the factory is the command, `uvm\_component\_utils(test2).

Just like test1, when test2 is executed, it will be the first component built after executing the run\_test() command in the top module. All of the tests in this example will reference the factory to build the env and the command that accesses the env type from the factory is the command:

```

e = env::type_id::create("e", this);

```

test2 also includes a command to change the transaction type that is returned whenever the

trans type is requested. The test2 code instructs the factory to override the return type of the

transaction from trans to trans2. The UVM command to perform this action is:

set\_type\_override\_by\_type(trans::get\_type(), trans2::get\_type());

All components and sequences built in this test will now create a **trans2** type whenever **trans** is requested. This is a powerful technique that allows engfineers to reuse testbench sequences and components without modifying the original source files. This is why UVM uses a factory!

```

class test2 extends uvm_test;

`uvm_component_utils(test2)

env e;

function new (string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build phase(uvm phase phase);

super.build phase(phase);

set_type_override_by_type(trans::get_type(), trans2::get_type());

e = env::type_id::create("e", this);

endfunction

function void end_of_elaboration_phase(uvm_phase phase);

super.end_of_elaboration_phase(phase);

this.print();

factory.print();

endfunction

task run_phase(uvm_phase phase);

trans sequence seq;

phase.raise objection(this);

seq = trans_sequence::type_id::create("seq");

seq.start(e.agnt.sqr);

phase.drop_objection(this);

endtask

endclass

```

Example 14 - test2.sv test (factory version)

### Factory-based package - test2

In order to run the second test with the override transaction type, the tb\_pkg must also be modified to include the trans2.sv file and the test2.sv file, as shown in Example 15.

```

`ifndef TB PKG

`define TB_PKG

`include "uvm macros.svh"

package tb_pkg;

import uvm_pkg::*;

`include "trans.sv"

`include "trans2.sv"

// *NEW*

`include "tb_driver.sv"

`include "tb_sequencer.sv"

`include "tb_agent.sv"

`include "env.sv"

`include "trans_sequence.sv"

`include "test1.sv"

`include "test2.sv" // *NEW*

endpackage

```

`endif

Example 15 - tb\_pkg2.sv package file

### test2 structure and factory types reports

The test2 code included the same end\_of\_elaboration\_phase() request to execute the this.print() and factory.print() methods as were used in the test1 code. The corresponding testbench struction is shown in Figure 5 and the factory types registered for test2 now include the trans2 and test2 types, as shown in Figure 6.

UVM\_INFO /home/uvm/src/base/uvm\_root.svh(355) @ 0: reporter [NO\_DPI\_TSTNAME] UVM\_NO\_DPI defined--getting UVM\_TESTNAME directly, without DPI UVM\_INFO @ 0: reporter [RNTST] Running test test2...

| Туре                   | Size                                                                                                                                                                                        | Value                                                                                                                                                                                                       |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| test2                  | _                                                                                                                                                                                           | @491                                                                                                                                                                                                        |

| env                    | _                                                                                                                                                                                           | @501                                                                                                                                                                                                        |

| tb_agent               | _                                                                                                                                                                                           | @510                                                                                                                                                                                                        |

| tb_driver              | -                                                                                                                                                                                           | @520                                                                                                                                                                                                        |

| uvm_analysis_port      | _                                                                                                                                                                                           | @537                                                                                                                                                                                                        |

| uvm_seq_item_pull_port | _                                                                                                                                                                                           | @528                                                                                                                                                                                                        |

| tb_sequencer           | _                                                                                                                                                                                           | @546                                                                                                                                                                                                        |

| uvm_analysis_export    | -                                                                                                                                                                                           | @554                                                                                                                                                                                                        |