World Class Verilog, SystemVerilog & OVM/UVM Training

# **UVM Transactions - Definitions, Methods and Usage**

Clifford E. Cummings Sunburst Design, Inc. cliffc@sunburst-design.com www.sunburst-design.com

#### ABSTRACT

Fundamental questions most novice UVM users have include: Why uses classes instead of structs to define transactions for verification environments? What are advantages of using classes to represent transactions in a verification environment? What methods should be defined in a UVM transaction class and why are there both field macros and do\_methods() for creating the transaction methods?

This paper will detail advantages related to using class-based transactions and answer questions about why there is so much confusion surrounding transaction method definitions and usage. This paper will also detail transaction method usage and field definition guidelines and tradeoffs.

UVM Transactions - Definitions, Methods and Usage

# **Table of Contents**

| 1.                                         | Intr                         | oduction                                                                         | 7  |  |  |

|--------------------------------------------|------------------------------|----------------------------------------------------------------------------------|----|--|--|

| 2.                                         | 2. Classes -vs- structs      |                                                                                  |    |  |  |

| <ol> <li>Transaction class types</li></ol> |                              |                                                                                  |    |  |  |

|                                            | .2.                          | UVM transactions                                                                 |    |  |  |

| 3                                          | .3.                          | Unnecessary Output Randomization                                                 |    |  |  |

| 4. UVM transaction types                   |                              |                                                                                  |    |  |  |

|                                            | .1.                          | Standard class formatting                                                        |    |  |  |

| 5.                                         | 5. Transaction class methods |                                                                                  |    |  |  |

| 6.                                         | Intr<br>.1.                  | oduction to standard transaction methods<br>Factory registration of transactions |    |  |  |

|                                            | .2.                          | <pre>`uvm_object_utils() -vs- `uvm_object_utils_begin()/_end</pre>               |    |  |  |

|                                            | .3.                          | m_uvm_field_automation() method                                                  |    |  |  |

|                                            | .4.                          | Proposed Future UVM Macro Change                                                 |    |  |  |

| 7.                                         |                              | erited standard transaction methods                                              |    |  |  |

| 7                                          | .1.                          | Should I override the standard transaction methods?                              |    |  |  |

| 7                                          | .2.                          | Inherited transaction utility methods                                            | 20 |  |  |

| 7                                          | .3.                          | create() method                                                                  | 20 |  |  |

| 7                                          | .4.                          | clone() method                                                                   | 21 |  |  |

| 7                                          | .5.                          | convert2string()                                                                 | 21 |  |  |

| 7                                          | .6.                          | Plan for extended convert2string() methods                                       | 22 |  |  |

| 7                                          | .7.                          | Transaction printAll() method??                                                  | 23 |  |  |

| 8.                                         | -                            | _methods()                                                                       |    |  |  |

| -                                          | .1.                          | Virtual method rules and virtual do_ <i>method()</i> prototypes                  |    |  |  |

|                                            | .2.                          | base-class casting to extended class handle                                      |    |  |  |

|                                            | .3.                          | rhs & rhs_ do_ <i>method()</i> arguments                                         |    |  |  |

|                                            | .4.                          | uvm_object default do_ <i>methods</i> ()                                         |    |  |  |

|                                            | .5.                          | copy() and do_copy()                                                             |    |  |  |

|                                            | .6.                          | Using the copy() method: to_tr.copy(from_tr)                                     |    |  |  |

|                                            | .7.                          | print(), sprint() and do_print()                                                 |    |  |  |

|                                            | .8.                          | record() and do_record()                                                         |    |  |  |

|                                            | .9.                          | pack() and do_pack()                                                             |    |  |  |

|                                            | .10.                         | unpack() and do_unpack()                                                         |    |  |  |

| 8                                          | .11.                         | compare() and do_compare()                                                       | 55 |  |  |

| 8.12. uvm_comparer policy class methods                                      |

|------------------------------------------------------------------------------|

| 8.13. do_methods & super.do_methods()                                        |

| 8.14. Templates with do_methods()                                            |

| 9. Field macros                                                              |

| 9.1. Field macro types                                                       |

| 9.2. Field macro flags                                                       |

| 9.3. Combining Field Macros with do_methods() 50                             |

| 10. Benchmarks                                                               |

| 10.1. Benchmarking methodology                                               |

| 10.2. Benchmarking do_methods() with nonrand-outputs and rand-outputs        |

| 10.3. Benchmarking field macros with nonrand-outputs and rand-outputs        |

| 11. Summary & Conclusions                                                    |

| 12. Acknowledgements                                                         |

| 13. References:                                                              |

| 14. AUTHOR & CONTACT INFORMATION                                             |

| 15. Appendix A                                                               |

| 15.1. UVM classes parameterized to uvm_sequence_item                         |

| 15.2. UVM classes parameterized to int                                       |

| 16. Appendix B                                                               |

| 16.1. Benchmark files to test simulation efficiency                          |

| 16.2. Benchmark vcs_benchmark_times file65                                   |

| 16.3. Benchmark test1 file with repeat-loop                                  |

| 16.4. trans1f - randomized outputs - uses field macros - no UVM_ALL_ON flags |

# **Table of Tables**

| Table 1 - uvm_comparer methods                                                   | 37 |

|----------------------------------------------------------------------------------|----|

| Table 2 - Field macros defined in UVM                                            | 43 |

| Table 3 - UVM field macro flag parameters defined in base/uvm_object_globals.svh | 45 |

| Table 4 - UVM field macro onehot flag settings in base/uvm_object_globals.svh    | 46 |

# **Table of Figures**

| Figure 1 - Transaction passing                                                                     |

|----------------------------------------------------------------------------------------------------|

| Figure 2 - Standard class formatting 10                                                            |

| Figure 3 - Transaction formatting w/ field macros                                                  |

| Figure 4 - Transaction formatting w/ do_methods()11                                                |

| Figure 5 - Actual `define uvm_object_utils macro definition                                        |

| Figure 6 - Actual `define uvm_object_utils_begin macro definition 13                               |

| Figure 7 - Actual `define uvm_object_utils_end macro definition                                    |

| Figure 8 - Illegal Syntax - Calling both `uvm_object_utils() and `uvm_field_utils_begin() 14       |

| Figure 9 - Proposed UVM Change - new definition for `uvm_object_utils(T) 16                        |

| Figure 10 - Important, inherited utility non-virtual methods                                       |

| Figure 11 - Standard transaction methods - two ways to create them                                 |

| Figure 12 - Important utility non-virtual method prototypes 17                                     |

| Figure 13 - UVM 1.1d - src/base/uvm_object.svh - compare() method implementation 19                |

| Figure 14 - Important, inherited utility virtual methods 20                                        |

| Figure 15 - Important utility virtual method prototypes                                            |

| Figure 16 - uvm_object create() method - manual definition                                         |

| Figure 17 - uvm_object source code for convert2string()                                            |

| Figure 18 - Extended transaction function calls to super.output2string() & super.input2string() 23 |

| Figure 19 - Creating the standard transaction methods by overriding the built-in do_methods() 24   |

| Figure 20 - Inherited do_method() hooks to define standard transaction methods                     |

| Figure 21 - Overriding the do_copy() and do_compare() methods with uvm_object inputs 26            |

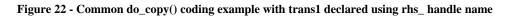

| Figure 22 - Common do_copy() coding example with trans1 declared using rhs_ handle name. 27        |

| Figure 23 - Preferred do_copy() coding example with trans1 declared using tr handle name 27        |

| Figure 24 - Transaction copy() and compare() methods - common usage block diagram                  |

| Figure 25 - Example sb_predictor.sv - collecting transactions using the tr.copy() method 29        |

| Figure 26 - do_copy() inherited virtual method prototype and source code                           |

| Figure 27 - trans1 example with do_copy() and do_compare() methods defined 30                      |

| Figure 28 - NULL do_print() method                                                                 |

| Figure 29 - do_print() inherited virtual method prototype and source code                          |

| Figure 30 - do_record() inherited virtual method prototype and source code                         |

| Figure 31 - do_pack() inherited virtual method prototype and source code                           |

| Figure 32 - do_unpack() inherited virtual method prototype and source code                    |

|-----------------------------------------------------------------------------------------------|

| Figure 33 - do_compare() inherited virtual method prototype and source code                   |

| Figure 34 - Example sb_comparator.sv - comparing transactions using out_tr.compare(exp_tr) 35 |

| Figure 35 - do_compare() method that does not use the uvm_comparer                            |

| Figure 36 - do_compare() method that DOES use the uvm_comparer methods                        |

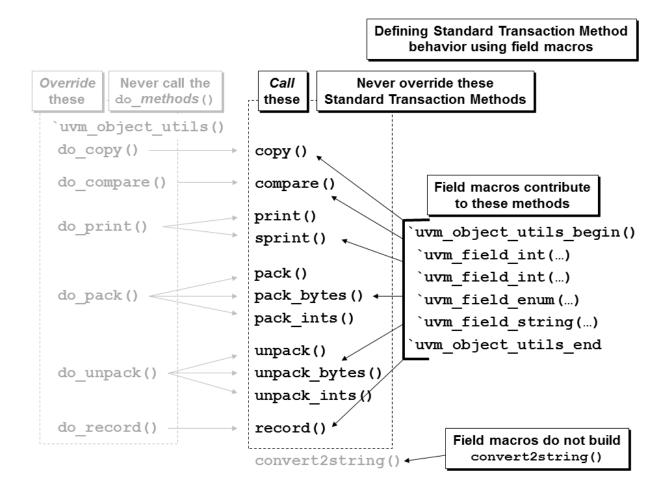

| Figure 37 - Non-comparer output -vs- uvm_comparer reported messages                           |

| Figure 38 - Example trans1.sv template file with do_copy() & do_compare() templates           |

| Figure 39 - Creating the standard transaction methods by using the UVM field macros           |

| Figure 40 - Creating the standard transaction methods by using the field macros               |

| Figure 41 - ERROR - combining variables into a single field macro - VCS error shown           |

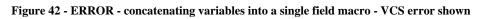

| Figure 42 - ERROR - concatenating variables into a single field macro - VCS error shown 42    |

| Figure 43- UVM field macro onehot flag settings diagram                                       |

| Figure 44 - Field macro flags implicitly enable UVM_ALL_ON                                    |

| Figure 45 - trans2 legally defined using multiple +-separated field macro flags               |

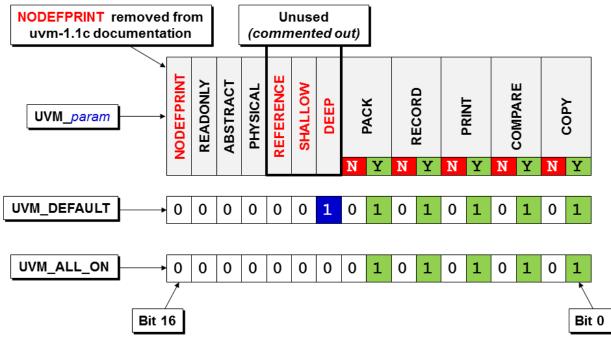

| Figure 46 - test2: copies and compares trans2 objects                                         |

| Figure 47 - test2 simulation output - b-variable comparison fails as expected                 |

| Figure 48 - UVM_NOCOPY flag accidentally  -specified twice - nocopy remains active            |

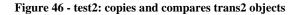

| Figure 49 - UVM_NOCOPY flag accidentally +-specified twice - removing the nocopy setting49    |

| Figure 50 - trans8b base with field macros extended in trans8 with do_methods() 50            |

| Figure 51 - Benchmark test1.sv run_phase() with randomize(), copy() and compare() loop 52     |

| Figure 52 - Common benchmark trans1 code                                                      |

| Figure 53 - Benchmark script to run the first transactions five times                         |

| Figure 54 - First benchmark trans1 with non-rand outputs and do_methods()                     |

| Figure 55 - Third benchmark trans1 with non-rand outputs and field macros                     |

| Figure 56 - UVM classes parameterized to the uvm_sequence_item type                           |

| Figure 57 - UVM classes parameterized to the int type                                         |

| Figure 58 - vcs_benchmark_times report file for a loop CNT=10,000,000                         |

# **Table of Examples**

| Example 1 - File: tb_pkg1a.sv                                                                  |

|------------------------------------------------------------------------------------------------|

| Example 2 - File: run1a.f                                                                      |

| Example 3 - File: tb_pkg1b.sv                                                                  |

| Example 4 - File: run1b.f                                                                      |

| Example 5 - File: tb_pkg1c.sv                                                                  |

| Example 6 - File: run1c.f                                                                      |

| Example 7 - File: tb_pkg1d.sv                                                                  |

| Example 8 - File: run1d.f                                                                      |

| Example 9 - File: tb_pkg1e.sv                                                                  |

| Example 10 - File: run1e.f                                                                     |

| Example 11 - File: tb_pkg1f.sv                                                                 |

| Example 12 - File: run1f.f                                                                     |

| Example 13 - File: doit1a.vcs                                                                  |

| Example 14- File: doit1b.vcs                                                                   |

| Example 15- File: doit1c.vcs                                                                   |

| Example 16- File: doit1d.vcs                                                                   |

| Example 17- File: doit1e.vcs                                                                   |

| Example 18 - File: doit1f.vcs                                                                  |

| Example 19 - File: report.vcs - gathers benchmark simulation times                             |

| Example 20 - File: doitall.vcs - execute after setting loop CNT value in the CNT_file file 64  |

| Example 21 - trans_printing.sv - common printing methods included in each trans1 class 64      |

| Example 22 - File: top.sv - wrapper top-module to permit testing                               |

| Example 23 - File: CNT_file - holds loop-CNT value                                             |

| Example 24 - File: test1.sv - randomizes, copies and compares in a repeat(`CNT) loop           |

| Example 25 - File: trans1a.sv - no rand outputs - uses do_methods() - no field macros67        |

| Example 26- File: trans1b.sv - rand outputs - uses do_methods() - no field macros 68           |

| Example 27 - File: trans1c.sv - no rand outputs - uses field macros - no do_methods() 69       |

| Example 28- File: trans1d.sv - rand outputs - uses field macros - no do_methods()              |

| Example 29 - File: trans1e.sv - no rand outputs - uses do_methods() - no super.do_methods() 71 |

| Example 30 - File: trans1f.sv - no rand outputs - uses field macros - no UVM_ALL_ON flags. 72  |

## 1. Introduction

All advanced class-based verification methodologies use classes to represent transactions, but why? Why not use structs?

To advanced users the answers are obvious but to novice users the questions never seem to be addressed in any literature. The problem is, most existing UVM texts and reference guides were written by really, really smart software engineers that assume that all users naturally know the answer to this and many other questions, which is not a valid assumption.

The first step to understand the answers to these questions is to compare class-based transaction capabilities to struct-based transaction capabilities.

This paper will also go into detail on the creation of transaction classes with standard transaction methods. The methods will be created using two techniques, (1) do\_methods() and (2) UVM field macros.

# 2. Classes -vs- structs

New users often ask the question, why use class types instead of structs for verification?

To better understand why classes are used instead of structs, it is useful to compare the different capabilities between classes and structs in SystemVerilog.

- Classes and structs both have multiple fields.

- Classes can have randomized fields while struct fields cannot be automatically randomized.

- Classes can include randomization constraints while structs cannot include automatic randomization constraints.

- Classes can have important built-in methods while structs cannot have built-in methods.

- Classes are a dynamic type and you can generate as many as you need at runtime while structs are a static type and the user must anticipate and statically declare all required structs at the beginning of the simulation.

- Class types can be extended while new versions of a struct must be copied from the original version and new fields added.

- Classes can be put into a UVM factory for easy runtime substitution while structs cannot.

Classes are basically dynamic, ultra-flexible structs that can be easily randomized, easily control the randomization, and be created whenever they are needed. Classes have the multiple field encapsulation capability that exist in structs, plus so much more. That is why classes are the preferred structure to represent testbench transactions.

Another advantage shared by both classes and structs is that they are passed around the testbench as a unit, whether there is one signal or 1,000 signals in the transaction, so it is easy to pass signals around the testbench environment with single unit operations. If signals are added or removed from the transaction, most of the testbench structure requires no modification. There are

just a few testbench components that need to interact with all of the component signals individually. Some of those components will be discussed in later sections.

# 3. Transaction class types

Once it is accepted that transactions should be class types, the next question is what should UVM transaction classes be? UVM testbench transactions are all extensions of the uvm\_sequence\_item type, which is a derivative of the uvm\_object type, and uvm\_object is the base class type for all UVM components and transactions (not counting the uvm\_void type).<sup>1</sup>

## 3.1. Class parameter types: uvm\_sequence\_item & int

The default transaction type for UVM components parameterized to a transaction type and the uvm\_sequence type is the uvm\_sequence\_item type. Example component types that are parameterized to uvm\_sequence\_item include uvm\_driver and uvm\_sequencer. All user transactions will be derivatives of the uvm\_sequence\_item type.

A complete list of the eight UVM classes that are parameterized to the uvm\_sequence\_item type is shown in Appendix A on page 59.

The default type for many of the other UVM base class types parameterized to a transaction type is the 32-bit, 2-state int type.

*NOBODY* would ever us the *int* type as a transaction type. The *int* type is just the default, type-based, place holder inside of parameterized classes to make sure the class-based UVM library will compile correctly. EVERYBODY replaces the *int* type, typically with a class-based transaction type. Examples of commonly used components that are parameterized to the *int* type include uvm\_tlm\_fifo and uvm\_analysis\_tlm\_fifo.

A complete list of the 69 UVM base classes that are parameterized to the *int* type is also shown in Appendix A on page 59.

## 3.2. UVM transactions

When approaching class-based verification for the first time a verification engineer is tempted to create one transaction type for the inputs and another transaction type for the outputs, because verification engineers who have done directed testing are accustomed to sending inputs into the design and then sampling the outputs for verification purposes.

When comparing UVM transactions to directed testing methods, transactions have fields for both inputs and outputs in the same transaction, while directed testing separates the input fields from the output fields. This is an important point when initially learning class-based verification.

<sup>&</sup>lt;sup>1</sup> **uvm\_void** is the root base class for all UVM components and transactions, but it is an empty virtual class that is extended to create the **uvm\_object** base class. Nobody works with **uvm\_void** but **uvm\_object** is extensively used within all UVM testbenches.

In a UVM testbench environment the agent includes both a driver and a monitor. Even though the driver is given a copy of an entire transaction object that includes both inputs and outputs, the driver collects and only sends the transaction inputs to the design under test (DUT). The transaction outputs are ignored by the driver. The driver is one of the testbench components that must extract and properly send the individual input signals to the DUT.

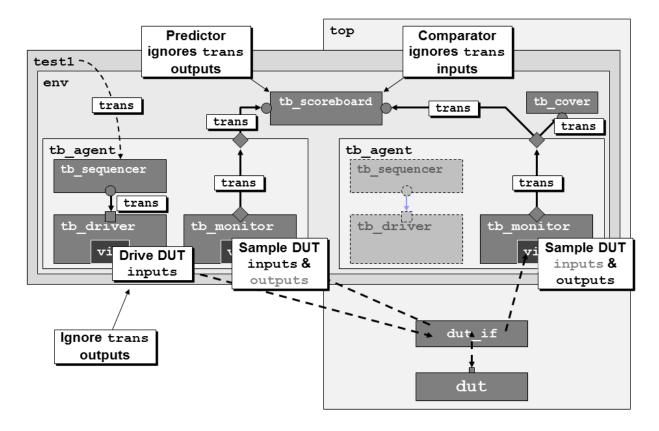

The monitor actually samples both inputs and outputs from the DUT interface. The driver side agent has a monitor that will sample both the inputs and outputs but only the inputs will be processed by to the predictor inside of a scoreboard as noted in Figure 1. The sampled outputs are still in that transaction but they are completely ignored.

The output-side agent uses the exact same monitor, which samples both the inputs and the outputs from the DUT interface, but on the output-side monitor, even though both the inputs and outputs have been sampled and sent to the scoreboard, the inputs will be discarded by the comparator in the scoreboard as noted in Figure 1 and the actual DUT outputs will be used for comparison against the predicted outputs.

Figure 1 - Transaction passing

The novice UVM verification user is tempted to create two different types of transactions, one that only holds sampled inputs and another that only holds sampled outputs, but if two different transaction types are used in two different monitors it means that the agent is not reusable on

both the stimulus-driving and output-sampling sides of the environment. By sampling both inputs and outputs in the same monitor and discarding the outputs on the stimulus-driving side and the inputs on the output-sampling side, we can reuse the exact same monitoring agents.

Understanding this technique explains how the same transaction can be used on both the inputside and output-side of the verification environment. This technique is typically unknown to engineers who have only done Verilog directed testbenches in the past.

#### 3.3. Unnecessary Output Randomization

If the transaction class has separately defined output and input variables, there is no need to randomize the output variables.

The randomized inputs will be sent to the DUT while any randomized outputs would just be discarded; hence, randomization of outputs would just be an inefficient additional simulation step.

# 4. UVM transaction types

As previously mentioned, all user-defined transaction types should be extended from the uvm\_sequence\_item type, and the uvm\_sequence\_item class type is a derivative of the uvm\_object class type.

#### 4.1. Standard class formatting

Although not required by UVM, I prefer to follow a standard code-layout for my UVM testbench components and UVM transaction definitions. A standard format helps with the readability of the code and helps me to quickly find important sections of the code. The formatting steps and order that I follow are shown in Figure 2.

```

(0) Declare transaction variables

(if field macros are used)

(1) Register class with factory

Optional: declare field macros | (mostly in transactions)

(2) Declare variables & covergroups | (if any)

(3) Declare virtual interface

(if any)

(4) Declare ports & components

(if any)

(5) Standard new() constructor

(if any)

(6) build_phase()

(7) connect_phase()

(if any)

(8) Other pre-run phases

(if any)

(if any)

(9) run_phase()

(10) Other post-run phases

(if any)

(11) Common component methods

(if any)

```

Figure 2 - Standard class formatting

As noted, the above format and order is not only used for transactions but also for testbench components. For transactions, there are no phase methods, so my preferred order looks like this:

#### Using Field Macros

- (0) Declare transaction variables

- (1) Register class with factory and declare field macros

- (2) Declare vars & covergroups

- (5) Standard new() constructor

- (11) Common transaction methods

- convert2string() method

Figure 3 - Transaction formatting w/ field macros

Using do\_methods()

```

(1) Register class with factory

(2) Declare vars & covergroups

(5) Standard new() constructor

(11) Common transaction methods

convert2string() methods

do_copy() / do_compare() /

other do_methods()

```

Figure 4 - Transaction formatting w/ do\_methods()

The differences between using field macros and do\_methods() will be described in later sections.

## 5. Transaction class methods

One of the advantages of using transaction classes is that they can contain important utility methods. These important methods remove many coding requirements that existed in Verilog testbenches.

There are two ways to implement important transaction methods: the first is to use field macros, the second is to use manual coding techniques by overriding the built-in do\_methods().

Using field macros is relatively simple but they can be inefficient during simulation and difficult to debug if something does go wrong. The UVM User Guide[8] was largely written by Cadence UVM experts and Cadence recommends using these field macros. Mentor UVM experts typically recommend that verification engineers avoid using the field macros due to their coding and simulation inefficiencies.[1][3][5][12]

Unfortunately, the UVM User Guide only documents the use of field macros and does not include any documentation about an alternate approach, that of using the do\_methods() to define the standard transaction methods. Similarly, the Verification Academy [12] only shows the use of do\_method() overrides to define the standard transaction methods and does not demonstrate the alternate approach of using field macros. Verification engineers that reference these two sources are often perplexed about the divergent recommendations and this becomes a source of much confusion to novice UVM users. It would have been better if the two major sources of information had promoted their preferred approach and then acknowledge that there was an alternate method. Adam Erickson's paper on "Evil Macros"[1] discusses both approaches and promotes the use of the do\_methods(), while many of my professional colleagues prefer the ease-of-use of the field macros.

Overriding the built-in do\_methods() requires more manual coding by the verification engineer but the overridden do\_methods() are more simulation efficient and not too difficult to code once a few important techniques are understood.

Both of these techniques will be described in later sections.

## 6. Introduction to standard transaction methods

In this paper, the important convenience functions are referred to as standard transaction methods.

The standard transaction methods are zero-time functions that should be defined in a transaction class and should always include user defined copy(), compare() and convert2string() methods. One other method that is important to define is the print() function, just because many users expect it to be available, even though convert2string() is often both more simulation and more print-space efficient.

If the design includes serial-to-parallel or parallel-to-serial activities that are very common among network packet-based designs, additional functions that will be included in the standard transaction function list, include: pack() and unpack(). One other standard transaction function is the record() function that is somewhat tool specific and used to help debug transient transaction objects.

The user should never override the standard transaction methods directly, but instead should indirectly define the required methods by overriding the base class do\_methods() or by implementing field macros.

Each user transaction class that extends from uvm\_sequence\_item inherits the standard transaction methods, which are mostly-empty methods defined in the uvm\_object virtual base class. One or more of these methods should be either directly or indirectly defined in the user transaction class.

## 6.1. Factory registration of transactions

The user's transaction class must be registered with the factory.

If you are going to create the standard transaction methods by overriding the built-in do\_methods() you must use the `uvm\_object\_utils() macro.

If you are going to create the standard transaction methods by using field macros, you must use the `uvm\_object\_utils\_begin() / `uvm\_object\_utils\_end macros.

What is different about these macros? The details are described in `uvm\_object\_utils() -vs-`uvm\_object\_utils\_begin()/\_end section.

## 6.2. `uvm\_object\_utils() -vs- `uvm\_object\_utils\_begin()/\_end

In the UVM src/macros/uvm\_object\_define.svh file, there exists two forms of `uvm\_object\_utils() macros to register the transaction with the factory, along with other important transaction class based setup. The pertinent code is shown below.

```

`define uvm_object_utils(T) \

`uvm_object_utils_begin(T) \

`uvm_object_utils_end

```

Figure 5 - Actual `define uvm\_object\_utils macro definition

The first observation to make is that calling `uvm\_object\_utils(T) is equivalent to calling the back-to-back commands `uvm\_object\_utils\_begin(T) / `uvm\_object\_utils\_end. If a transaction is defined using the `uvm\_object\_utils(T) macro, no field macros are permitted in the transaction class definition. This is the technique recommended by Mentor UVM experts.[1][3]

As shown below, the `uvm\_object\_utils\_begin(T) macro actually implements some important user-transaction functionality, including:

| `m_uvm_object_registry_internal     | - register the transaction class with the factory   |

|-------------------------------------|-----------------------------------------------------|

| `m_uvm_object_create_func           | - define the create() method for this class         |

| `m_uvm_get_type_name_func           | - define the get_type_name() method for this class  |

| <pre>`uvm_field_utils_begin()</pre> | - prepares to process defined field macros, if used |

The actual `uvm\_object\_utils\_begin(T) macro definition is shown in Figure 6.

```

`define uvm_object_utils_begin(T) \

`m_uvm_object_registry_internal(T,T) \

`m_uvm_object_create_func(T) \

`m_uvm_get_type_name_func(T) \

`uvm_field_utils_begin(T)

```

Figure 6 - Actual `define uvm\_object\_utils\_begin macro definition

If the `uvm\_object\_utils() macro is used, the `uvm\_field\_utils\_begin() macro, which prepares the appropriate setup code for using field macros, is not populated with any field macros. As stated earlier, the `uvm\_object\_utils() macro should only be used if important transaction class methods are defined by overriding the do\_methods().

The `uvm\_field\_utils\_begin() macro defines a few functions important to field macros then opens a function definition that will be populated by field macros, if used.

The `uvm\_object\_utils\_end macro simply closes off the `uvm\_field\_utils\_begin() macro using a macro name that intuitively finishes the field\_utils block. The actual (and trivial) `uvm\_object\_utils\_end macro definition is shown in Figure 7.

```

`define uvm_object_utils_end \

end \

endfunction

```

Figure 7 - Actual `define uvm\_object\_utils\_end macro definition

Unfortunately, because there are two different macros to register the transaction with the factory, there are also two different coding styles that are commonly used to define transactions and the style chosen depends on whether do\_method() overrides or field macros are employed.

When I use the do\_method() style, the transaction class definition resembles this:

```

class trans1 extends uvm_sequence_item;

`uvm_object_utils(trans1) -- `uvm_object_utils() before declaration

<declare variables>

<standard constructor>

<override do_methods()>

```

It is annoying that I must use two different `uvm\_object\_utils() placements just because I choose to use do\_methods() or field macros, but the field macro style requires the variables to be declared before they are referenced by field macros, where the declared field macros must be encapsulated within the `uvm\_object\_utils\_begin(T) / `uvm\_object\_utils\_end pair.

It is certainly possible to place the `uvm\_object\_utils() macro call after declaring variables when using the do\_methods() style, but I prefer to see my `uvm\_object\_utils() command at the top of the class definition, just beneath the class header, just as I do for all testbench component and sequences classes.

What I really want is a pair of macros to encapsulate the field macros without requiring that they be placed within a `uvm\_object\_utils\_begin(T) / `uvm\_object\_utils\_end pair, perhaps macros called `uvm\_field\_utils\_begin() / `uvm\_field\_utils\_end. From Figure 6 shown on page 13, I saw that these macros already existed! So I tried placing the `uvm\_object\_utils() macro at the top of the transaction class, declared variables, and tried using `uvm\_field\_utils\_begin() with field macro declarations, as shown in Figure 8.

```

class trans1 extends uvm_sequence_item;

`uvm_object_utils(trans1)

rand bit [7:0] q;

rand bit [7:0] a, b, c;

`uvm_field_utils_begin(trans1) // ** Error this line

`uvm_field_int(q, UVM_ALL_ON)

`uvm_field_int(a, UVM_ALL_ON)

`uvm_field_int(b, UVM_ALL_ON)

`uvm_field_int(c, UVM_ALL_ON)

`uvm_field_int(c, UVM_ALL_ON)

`uvm_field_int(c, UVM_ALL_ON)

`uvm_field_utils_end

....

```

Figure 8 - Illegal Syntax - Calling both `uvm\_object\_utils() and `uvm\_field\_utils\_begin()

Unfortunately, this did not work and the compiler reported the error:

\*\* Error: '\_\_m\_uvm\_field\_automation' already exists;

must not be redefined as a function.

The problem is that the `uvm\_object\_utils() macro also calls the `uvm\_field\_utils\_begin(T) macro, and since the `uvm\_field\_utils\_begin(T) macro defines the \_\_m\_uvm\_field\_automation function, the function is defined twice, which is illegal.

#### 6.3. \_\_m\_uvm\_field\_automation() method

The `uvm\_object\_utils\_begin() macro, defined in the uvm/src/macros/uvm\_object\_defines.svh file, defines the first 20 lines of an internal \_\_m\_uvm\_field\_automation() method and the `uvm\_object\_utils\_end macro defines the last 7 lines of the same macro. If field macros are used to define the standard transaction methods, each field macro contributes to the middle section of the \_\_m\_uvm\_field\_automation() method. For example, each call to the `uvm\_field\_int() macro adds 59 more lines of code to the middle of the \_\_m\_uvm\_field\_automation() macro.

The 59-line block of code added to the \_\_m\_uvm\_field\_automation() method is mostly a very large case() statement that executes the proper code for the case values of: UVM\_CHECK\_FIELDS, UVM\_COPY, UVM\_COMPARE, UVM\_PACK, UVM\_UNPACK, UVM\_RECORD, UVM\_PRINT and UVM\_SETINT. When the user calls the compare() method, the compare method actually calls the internally constructed \_\_m\_uvm\_field\_automation() method with the UVM\_COMPARE argument to execute the UVM\_COMPARE code in each of the added case() statements.

For each field macro defined, another large block of code is added to the middle of the internal\_m\_uvm\_field\_automation() method, and each block of code includes multiple calls to other methods within a \_\_m\_uvm\_status\_container class, so if there are ever any problems related to the field macros, the debugging task is extremely verbose and complex. Fortunately, the field macros work properly most of the time, but when they don't work, debugging is time-consuming and extremely frustrating.

## 6.4. Proposed Future UVM Macro Change

It seems that the previous `uvm\_field\_utils\_begin(T) macro problem described in section 6.2 could be easily fixed by modifying the definition for the `uvm\_object\_utils(T) macro. Instead of calling `uvm\_object\_utils\_begin(T) / `uvm\_object\_utils\_end, which calls four other macros, redefine `uvm\_object\_utils() to just call three of the macros, omitting the call to the `uvm\_field\_utils\_begin() macro, which appears to be completely unnecessary in a non-field macros transaction class definition. The newly proposed definition is shown in Figure 9.

```

`define uvm_object_utils(T) \

`m_uvm_object_registry_internal(T,T) \

`m_uvm_object_create_func(T) \

`m_uvm_get_type_name_func(T)

```

Figure 9 - Proposed UVM Change - new definition for `uvm\_object\_utils(T)

If it is determined that there are no backward compatibility issues, I request that the UVM Standards Committee implement this change. *Time to step off the soap box and get back to technical usage detail.*

## 7. Inherited standard transaction methods

The user's transaction class is extended from the uvm\_sequence\_item class, which is derived from the top-level uvm\_object class type. Through this inheritance path, the user's transaction class inherits the following important utility methods:

```

copy(),

compare(),

print(), sprint(),

pack(), pack_bytes(), pack_ints(),

unpack(), unpack_bytes(), unpack_ints(),

record()

```

Figure 10 - Important, inherited utility non-virtual methods

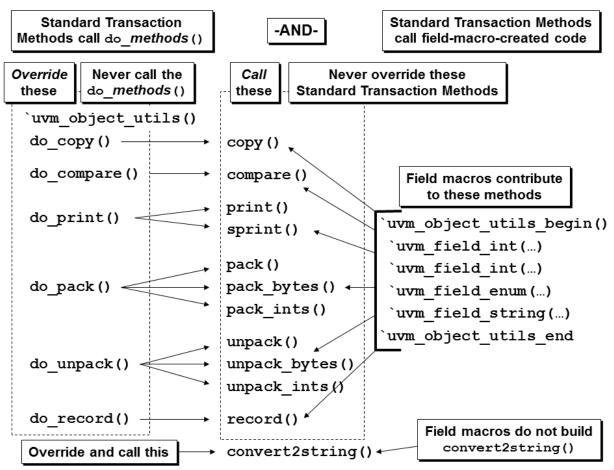

These 11 standard transaction methods are non-virtual functions or non-virtual void functions and the user should NEVER extend or override any of these important utility methods in a transaction class. These standard transaction methods execute a large amount of UVM overhead code and then call the <u>\_\_m\_uvm\_field\_automation()</u> method (which executes operations built from user-declared field macros) followed by calling do\_methods(), which can be overridden by the user, as shown in Figure 11.

As described in the preceding paragraph, it is important to note that calling any of the standard transaction methods actually executes both field macro code AND the corresponding do\_methods(). The significance of this fact is that an engineer can properly define field macros and then exclude the implementation of field macro functionality if that functionality is subsequently implemented using the corresponding do\_methods(). Conversely, it is very risky to implement any of the standard transaction methods by combining partial implementation using field macros and completing the implementation with a partial-functionality definition in a do\_method(). The latter is never seen in standard industry practice and is highly discouraged.

Figure 11 - Standard transaction methods - two ways to create them

The actual prototypes for these 11 methods are shown in Figure 12.

```

function void

copy

(uvm_object

rhs);

function bit

compare

(uvm_object

rhs, uvm_comparer comparer=null);

function void

record

uvm recorder recorder=null);

(

function void

uvm_printer printer =null);

print

(

uvm_printer printer =null);

function string sprint

function int pack

bit

bitstream [],

(ref

input uvm_packer

packer=null);

function int pack_bytes

(ref

byte unsigned bytestream[],

input uvm_packer

packer=null);

function int pack_ints

(ref

int unsigned intstream [],

packer=null);

input uvm_packer

function int unpack

(ref

bit

bitstream [],

input uvm packer

packer=null);

function int unpack_bytes (ref

byte unsigned bytestream[],

input uvm_packer

packer=null);

function int unpack_ints

(ref

int unsigned intstream [],

packer=null);

input uvm packer

```

Figure 12 - Important utility non-virtual method prototypes

#### 7.1. Should I override the standard transaction methods?

So why do I have to declare field macros or override do\_methods() to help implement the nonvirtual methods shown in Figure 10. Why don't I just override these standard transaction methods directly and bypass the field macros and do\_methods()?

Are you kidding? Have you seen the code for these methods in the uvm\_object.svh file??

WARNING: you should not take any time to try to read, examine or figure out the following 69 lines of compare() code from the uvm\_object base class. It is inserted into this paper to *discourage you from ever* considering the option to override the built-in compare() method. You should either use field macros or override the do\_compare() method.

```

1 // compare

2 // -----

3

4 function bit uvm object::compare (uvm object rhs,

uvm comparer comparer=null);

5

bit t, dc;

6

7

static int style;

8

bit done;

9

done = 0;

10

if(comparer != null)

11

__m_uvm_status_container.comparer = comparer;

12

else

13

<u>m_uvm_status_container.comparer = uvm_default_comparer;</u>

comparer = m uvm status container.comparer;

14

15

16

if(!__m_uvm_status_container.scope.depth()) begin

17

compare.compare_map.clear();

18

comparer.result = 0;

19

comparer.miscompares = "";

20

comparer.scope = __m_uvm_status_container.scope;

21

if(get name() == "")

22

__m_uvm_status_container.scope.down("<object>");

23

else

24

m uvm status container.scope.down(this.get name());

25

end

26

if(!done && (rhs == null)) begin

if(__m_uvm_status_container.scope.depth()) begin

27

28

comparer.print_msg_object(this, rhs);

29

end

30

else begin

31

comparer.print_msg_object(this, rhs);

32

uvm_report_info("MISCMP",

33

$sformatf("%0d Miscompare(s) for object %s@%0d vs. null",

34

comparer.result,

35

_m_uvm_status_container.scope.get(),

36

this.get_inst_id()),

37

m uvm status container.comparer.verbosity);

38

done = 1;

39

end

40

end

41

```

```

42

if(!done && (comparer.compare_map.get(rhs) != null)) begin

43

if(compare.compare_map.get(rhs) != this) begin

44

comparer.print_msg_object(this, comparer.compare_map.get(rhs));

45

end

46

done = 1; //don't do any more work after this case, but do cleanup

47

end

48

49

if(!done && comparer.check_type && (rhs != null) &&

50

(get_type_name() != rhs.get_type_name())) begin

51

__m_uvm_status_container.stringv = { "lhs type = \"", get_type_name(),

52

"\" : rhs type = \"", rhs.get_type_name(), "\""};

53

comparer.print_msg(__m_uvm_status_container.stringv);

54

end

55

56

if(!done) begin

57

comparer.compare_map.set(rhs, this);

58

__m_uvm_field_automation(rhs, UVM_COMPARE, "");

// LINE 58-field macros

59

dc = do_compare(rhs, comparer);

// LINE 59-do compare()

60

end

61

if( m uvm status container.scope.depth()==1) begin

62

63

__m_uvm_status_container.scope.up();

64

end

65

66

if(rhs != null)

comparer.print_rollup(this, rhs);

67

68

return (comparer.result == 0 && dc == 1);

69 endfunction

```

Figure 13 - UVM 1.1d - src/base/uvm\_object.svh - compare() method implementation

REMINDER: you should not take any time to try to read, examine or figure out the preceding 69 lines of compare() code. It is inserted into this paper to *discourage you from ever* considering the option to override the built-in compare() method. You should either use field macros or override the do\_compare() method. Anybody who tries to correctly override the built-in compare() method either needs to get-a-life or get-a-hobby! (Writing this paper makes me think that I need to get-a-life!!)

From the code in Figure 13, it can be seen that the default **compare()** method will make a call to implement the field macros (red-highlighted code on line 58) and will also call the user-defined **do\_compare()** method (red-highlighted code on line 59). Your job is to either define field macros or override the **do\_compare()** method and they will be automatically called by callbacks from the **compare()** method.

The problem you face if you try to override the compare() code is that there are 57 lines of important code before you either call the field macros on line 58, or call your implementation of the do\_compare() method on line 59 (both of which are embedded in an internal if-statement). Then you still need to add 10 more lines of code after field macros or do\_compare(). This means you cannot simply make a call to super.compare(). You would need something like a call to super.pre\_59\_lines\_compare(), add you compare code, then call something like a super.post\_10\_lines\_compare(), which of course is ridiculous!

There is similarly cryptic uvm\_object base class code for the other important standard transaction methods. The value of the existing field macros and do\_method() callbacks should now begin to be more obvious!

Guideline: do not directly override the copy(), compare() and other uvm\_object base class standard transaction methods.

#### 7.2. Inherited transaction utility methods

The user's transaction class, ultimately derived from the top-level uvm\_object class type, also inherits the 3 important utility methods shown in Figure 14.

```

create(),

clone(),

convert2string(),

Figure 14 - Important, inherited utility virtual methods

```

These 3 methods are virtual functions or virtual void functions. The actual prototypes for these 3 methods are shown in Figure 15.

```

virtual function uvm_object create (string name="");

return null;

endfunction

virtual function uvm_object clone ();

uvm_object tmp;

tmp = this.create(get_name());

if (tmp == null) `uvm_warning("CRFLD", "... create failed ...")

else        tmp.copy(this);

return(tmp);

endfunction

virtual function string convert2string();

return "";

endfunction

```

Figure 15 - Important utility virtual method prototypes

The virtual do\_methods() will be described in later sections, but the create(), clone() and convert2string() methods are described in the next three sections.

## 7.3. create() method

Per the UVM Class Reference manual, "Every class deriving from uvm\_object, directly or indirectly, must implement the create method."[7] When the `uvm\_object\_utils(T) macro is called, one of the actions of that macro is to automatically implement the create() method (the utils macro calls the `m\_uvm\_object\_create\_func(T) macro). If we do not call the `uvm\_object\_utils() macro, among other things, we would need to implement the create() method manually. A manual implementation example of the create() method from the UVM Class Reference manual is shown in Figure 16.

```

class mytype extends uvm_object;

...

virtual function uvm_object create(string name="");

mytype t = new(name);

return t;

endfunction

Figure 16 - uvm_object create() method - manual definition

```

Guideline: never manually implement the create() method. Call the `uvm\_object\_utils() macro to automatically implement the create() method.

#### 7.4. clone() method

By default, the clone() method calls the create() method (constructs an object of the same type) and then calls the copy() method. It is a one-step command to create and copy an existing object to a new object handle.

Guideline: never override the clone() method. The existing default behavior is good.

#### 7.5. convert2string()

The convert2string() method is one of the most important methods to define within a transaction. In the absence of a convert2string() method, each user has to decide how to print transaction values at different locations in the testbench.

The default convert2string() method defined in the uvm\_object virtual base class is basically a placeholder and just returns an empty string. The relevant code snippets for the uvm\_object base class convert2string() method are shown in Figure 17.

```

extern virtual function string convert2string();

...

function string uvm_object::convert2string();

return "";

endfunction

```

Figure 17 - uvm\_object source code for convert2string()

It is a common courtesy that the designer of every transaction class should override the convert2string() method with a well formatted string of the transaction variables. The convert2string() method is more efficient than calling the transaction print() method, which has to format the variables into table or tree-like formats.

Guideline: Every user-defined transaction method should include a convert2string() method.

By creating a **convert2string()** method, the transaction class developer is providing, to anybody who uses the transaction objects, the ability to print out the transaction object contents without the trouble to create their own display-type command.

The convert2string() method returns a formatted string of the transaction object's field contents. The convert2string() method should be called from a message macro, which also includes an "id" string field and a verbosity setting.

#### 7.6. Plan for extended convert2string() methods

The convert2string() method of a transaction class extended from a base transaction class will either need to reform all of the base class convert2string() transaction variables (discouraged) or call super.convert2string() to pick up the string information for the base transaction variables (preferred).

When printing, I prefer to group transaction inputs together followed by grouped transaction outputs. If you call super.convert2string(), you will probably have the extended input and output signals mixed with the base class input and output signals.

To avoid a mixed order of inputs and outputs, I recommend the creation of two more transaction functions called output2string() and input2string().

In the following example (Figure 18), trans2 extends trans1 and both classes have input2string() and output2string() methods. The extended class makes super.stringmethod() calls, concatenating extended variables to base class variables in the respective return statements:

```

intputs:

return ({super.input2string(), " ",s});

outputs:

return ({super.output2string(), " ",s});

The trans2 transaction class has a very simple definition for convert2string(), which

includes: return ({output2string(), " ", input2string()});

This way the inputs are grouped together and outputs are grouped together when printed.

```

```

class trans1 extends uvm_sequence_item;

`uvm_object_utils(trans1)

bit [7:0] a; // base output

rand bit [7:0] b; // base input

function string input2string();

return($sformatf("b=%2h", b));

endfunction

function string output2string();

return($sformatf("a=%2h", a));

endfunction

function string convert2string();

return ({input2string(), " ", output2string()});

endfunction

endclass

class trans2 extends trans1;

`uvm object utils(trans2)

bit [7:0] c; // extended output

22

```

```

rand bit [7:0] d; // extended input

...

function string input2string();

string s;

s = $sformatf("d=%2h", d);

return ({super.input2string()," ",s});

endfunction

function string output2string();

string s;

s = $sformatf("c=%2h", c);

return ({super.output2string()," ",s});

endfunction

function string convert2string();

return ({input2string(), " ", output2string()});

endfunction

endclass

```

Figure 18 - Extended transaction function calls to super.output2string() & super.input2string()

#### 7.7. Transaction printAll() method??

There are some examples in industry where the creators of transaction classes also create built-in **printAll()** methods that can be called directly without the need to call the **convert2string()** method from a `uvm\_info() macro. This is not recommended because although inserting a **printAll()** method into the transaction would certainly make printing transaction information easier, it unfortunately also semi-permanently fixes the "id" string and verbosity setting.

```

The convert2string() method returns a string value that should be called from a `uvm_info(), `uvm_error() or `uvm_fatal() message macro.<sup>2</sup>

```

There are times when you will want to report debug information and you will want to print transaction values with a verbosity setting of UVM\_DEBUG. At other times you will want the transaction values to print using the default UVM\_MEDIUM verbosity setting, while at other times you will want to only print successful transaction values if you enable the UVM\_HIGH verbosity setting. It is also useful to use unique "id" values in different places so that printing of some transactions can be masked while printing of other transactions can be promoted to always print.

If field macros are used, the built-in print() method will be populated, but when using the print() method the printed values will again be largely unmaskable and printed in a somewhat verbose multi-line table or tree format. For these reasons and for better verbosity control, I tend to skip the print() method in favor of the convert2string() method.

<sup>&</sup>lt;sup>2</sup> The `uvm\_warn message macro is almost worthless because it has a verbosity setting of uvm\_none and is therefore difficult to suppress. I prefer to use `uvm\_info message macros with different verbosity settings to replace the cumbersome `uvm\_warn message macro.

# 8. Do\_methods()

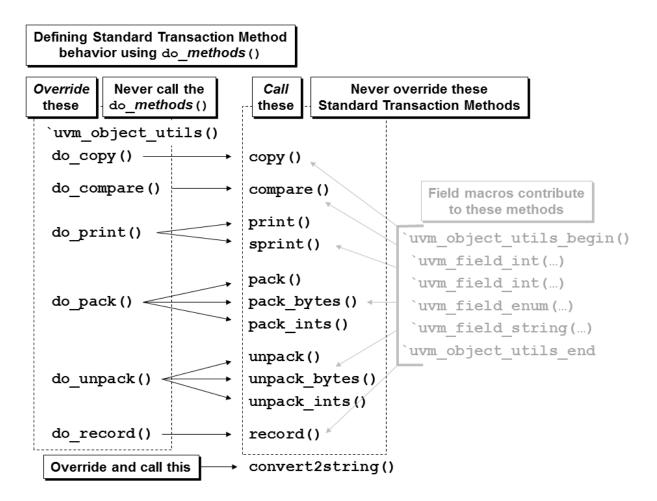

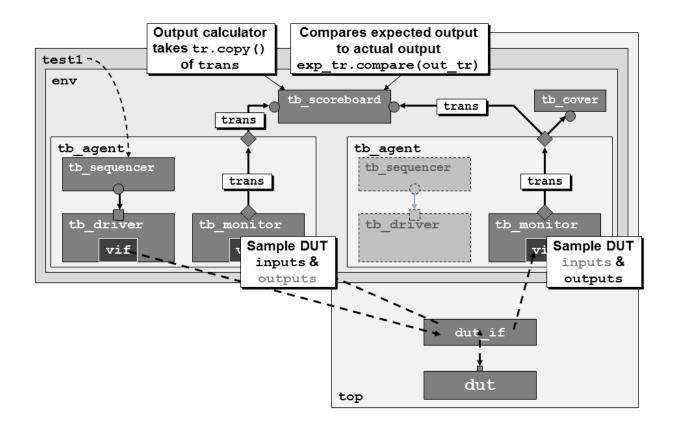

As was mentioned earlier, there are two ways to implement the important standard transaction methods. The standard transaction methods can be implemented using either the field macros or by overriding the built-in do\_methods() shown in Figure 20. This section describes the implementation of the standard transaction methods by overriding the do\_methods().

The 11 standard transaction methods shown in Figure 19 can be implemented by overriding the 6 do\_methods() also shown in Figure 19. The do\_methods() are empty callback methods defined in the uvm\_object base class. The user should never directly call any of the do\_methods(). The do\_methods() are called by the like-named, 11 standard transaction methods that are inherited from the uvm\_object base class.

Figure 19 - Creating the standard transaction methods by overriding the built-in do\_methods()

The user can override the built-in do\_methods(), shown in Figure 20, which will affect how the standard transaction methods behave when called.

```

do_copy()

do_compare()

do_print()

do_pack()

do_unpack()

do_record()

```

Figure 20 - Inherited do\_method() hooks to define standard transaction methods

#### 8.1. Virtual method rules and virtual do\_*method()* prototypes

All of the user-overridable do\_methods() are virtual methods, and SystemVerilog virtual methods have strict argument compatibility rules. When extending a SystemVerilog class and overriding a virtual method in an extended class, all argument types, names and return types must match the base class virtual method argument types and names, which means the method argument types and names cannot be changed.

This is simply a rule of object oriented languages like SystemVerilog and has nothing to do with the UVM methodology. UVM users must simply follow SystemVerilog rules and this is one of those rules.

Since all of the do\_methods() in the uvm\_object base class are virtual methods, overriding those methods in the user transaction class requires the user to use the exact same argument types and names.

#### 8.2. base-class casting to extended class handle

Nonspecific to UVM is the concept of assigning a base class handle to an extended class handle. Although it is a somewhat side-topic, it is an important topic when using UVM so it discussed in this section.

SystemVerilog permits direct assignment of an extended handle to a base handle. There might be multiple different extensions of the same base class type, and each extension can add unique variables and define different unique methods in the extended class. Since any of these extended class handles can be assigned to the base class handle, the newly assigned base handle cannot call the extended methods and variables that were added to extended classes since those variables and methods could be different from assignment to assignment and the base class can only guarantee existence of base methods and variables.

On the other hand, SystemVerilog does <u>NOT</u> permit direct assignment of a base class handle to a derived class handle because the derived class typically expects to access more variables and methods than existed in the base class definition and if the base class handle was assigned from a completely different extended object, the expected methods and variables might not exist. The base class handle type has no knowledge of the extended variables and methods.

If a constructed extended class object is assigned to a base class handle, the handle type is converted to the base class handle type and access to extended methods and extended variables is

UVM Transactions - Definitions, Methods and Usage not possible using the base class handle, even though the methods and variables still exist. If this base class handle is then \$cast<sup>3</sup> back to a declared extended class handle, then we again have access to the original variables, their values, and the extended methods. This is an important technique used with UVM standard do\_methods().

```

function void do_copy(uvm_object rhs);

trans1 tr;

if(!$cast(tr, rhs)) `uvm_fatal("trans1", "ILLEGAL do_copy() cast")

a = tr.a;

... (copy remaining variables)

endfunction

function bit do_compare(uvm_object rhs, uvm_comparer comparer);

trans1 tr;

bit

eq;

if(!$cast(tr, rhs)) `uvm fatal("trans1", "ILLEGAL do compare() cast")

eq = super.do compare(rhs, comparer);

eq \&= (a == tr.a);

... (compare remaining variables)

return(eq);

endfunction

```

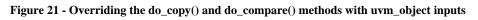

In Figure 21, the first three lines of the do\_copy() method and three of the first four lines of the do\_compare() method are standard required code. In all of the do\_methods(), the first argument of the prototype header is an input of the uvm\_object base class handle type, but when each do\_method() is called, they will be passed an extended trans1 transaction class handle, which will convert the trans1 transaction class handle into the rhs uvm\_object base class handle type.

Once a transl class handle has been converted into a uvm\_object base-class handle type, it is necessary to (1) declare a handle of the transl (derivative of uvm\_object) handle type, and then (2) \$cast the uvm\_object base class handle-type back into the transl (derivative) class handle type, to recover all of the transaction variables and gain access to the transaction methods that were hidden when the transaction handle was converted into a uvm\_object handle.

This is why the first few lines of each UVM standard do\_method() might look strange. This **\$cast**ing is simply a required step to recover all of the variables and methods of a transaction type, and is just SystemVerilog overhead code required by the UVM standard do\_methods().

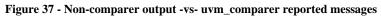

## 8.3. rhs & rhs\_do\_method() arguments

There are many industry example implementations of the do\_methods() where the trans1 (or equivalent) transaction class handle is declared with the handle name rhs\_ as shown in Figure 22. Then the do\_method() input argument rhs is \$cast to the trans1 rhs\_ handle. I

$<sup>^3</sup>$  \$cast performs checking. If the base class is holding a handle to a derived type that is different than the type being assigned, \$cast will fail. When \$cast is called as a task, this failure results in a tool-generated error message. When \$cast is called as a function, the failure results in a return status of 0 (a success returns 1).

personally believe this adds confusion to the code. It is too easy for the reader to miss the trailing "\_" on the **rhs**\_ handle and make incorrect assignments and assumptions.

```

function void do_copy(uvm_object rhs);

trans1 rhs_;

$cast(rhs_, rhs);

if(!$cast(rhs_, rhs)) `uvm_fatal("trans1", "ILLEGAL do_copy() cast")

a = rhs_.a;

... (copy remaining variables)

endfunction

```

The uvm\_object handle name of rhs in each of the standard transaction methods prototypes cannot be modified, but the commonly used transaction rhs\_ handle name can be changed. I prefer to replace the rhs\_ handle name with tr as shown in Figure 23, which is visibly distinct from the input rhs handle name.

```

function void do_copy(uvm_object rhs);

trans1 tr;

if(!$cast(tr, rhs)) `uvm_fatal("trans1", "ILLEGAL do_copy() cast")

a = tr.a;

... (copy remaining variables)

endfunction

```

$Figure \ \textbf{23-Preferred do\_copy}() \ coding \ example \ with \ trans1 \ declared \ using \ tr \ handle \ name$

I believe the code is more readable and less error prone by using the distinct tr handle name.

#### 8.4. uvm\_object default do\_methods()

The UVM top-level base class (at least the one we care about) is the uvm\_object class type. The uvm\_object virtual base class includes the following empty void virtual functions:

| do_copy()             | (Figure 26), |

|-----------------------|--------------|

| <pre>do_print()</pre> | (Figure 29), |

| do_record()           | (Figure 30), |

| do_pack()             | (Figure 31), |

| do_unpack()           | (Figure 32). |

The uvm\_object virtual base class also includes one almost-empty status-returning virtual function:

do\_compare() (Figure 33).

#### 8.5. copy() and do\_copy()

The built-in copy() method executes the <u>m\_uvm\_field\_automation()</u> method with the required copy code as defined by the field macros (if used) and then calls the built-in do\_copy() virtual function. The built-in do\_copy() virtual function, as defined in the uvm\_object base

class, is also an empty method, so if field macros are used to define the fields of the transaction, the built-in **copy()** method will be populated with the proper code to copy the transaction fields from the field macro definitions and then it will execute the empty **do\_copy()** method, which will perform no additional activity.

The copy() method can be used as needed in the UVM testbench. One common place where the copy() method is used is to copy the sampled transaction and pass it into a sb\_calc\_exp() (scoreboard calculate expected) external function that is frequently used by the scoreboard predictor[2] as shown in Figure 24.

Figure 24 - Transaction copy() and compare() methods - common usage block diagram

An example usage of the copy() method is shown in the scoreboard calculate-expected function of the sb\_predictor::sb\_calc\_exp() function in Figure 25. The transaction is passed through a uvm\_analysis\_port (originating from the tb\_monitor in the tb\_agent) to the sb\_calc\_exp() method in the sb\_predictor located inside the tb\_scoreboard class. The t transaction is then copied to a locally declared and created (line 4) transaction object (tr.copy(t); on line 14), then the calculated output value dout is copied to the transaction dout variable (tr.dout = dout; on line 18) and returned to the calling sb\_predictor component (line 19).

```

1 function trans1 sb_predictor::sb_calc_exp (trans1 t);

static logic [15:0] next_dout;

2

3

logic [15:0] dout;

4

trans1 tr = trans1::type_id::create("tr");

//-----

5

6

`uvm_info(get_type_name(), t.convert2string(), UVM_HIGH)

7

// async reset: reset the next dout AND current dout values -OR-

8

// non-reset : assign dout values & calculate the next dout values

9

dout = next dout;

10

if

(!t.rst_n) {next_dout,dout} = '0;

else if ( t.ld) next_dout

11

= t.din;

12

else if ( t.inc) next_dout++;

13

// copy all sampled inputs & outputs

14

tr.copy(t);

// overwrite the dout values with the calculated values.

15

16

// dout values were either calculated in the previous cycle

17

// or asynchronously reset in this cycle

18

tr.dout = dout;

19

return(tr);

20 endfunction

```

Figure 25 - Example sb\_predictor.sv - collecting transactions using the tr.copy() method

#### 8.6. Using the copy() method: to\_tr.copy(from\_tr)

The copy() method copies values from the from\_tr object to the variables in the to\_tr object (you are copying the values of variables from another transaction into this transaction). The transaction handle that is used to call the method name holds the destination variables. The transaction handle that is passed as an argument to the method holds the source variable values.

The default do\_copy() method defined in the uvm\_object virtual base class is empty. The relevant code snippets are shown in Figure 26.

```

extern virtual function void do_copy(uvm_object rhs);

...

function void uvm_object::do_copy(uvm_object rhs);

return;

endfunction

```

Figure 26 - do\_copy() inherited virtual method prototype and source code

The trans1 code with do\_copy() method used with the sb\_predictor class code of Figure 25 is shown in Figure 27.

```

class trans1 extends uvm_sequence_item;

`uvm_object_utils(trans1)

logic [15:0] dout; // outputs not randomized

rand bit [15:0] din;

rand bit rst_n;

```

```

function new (string name="trans1");

super.new(name);

endfunction

function void do_copy(uvm_object rhs);

trans1 tr;

if(!$cast(tr, rhs)) `uvm fatal("trans1", "ILLEGAL do copy() cast")

dout = tr.dout;

din = tr.din;

rst n = tr.rst n;

endfunction

function bit do_compare(uvm_object rhs, uvm_comparer comparer);

trans1 tr;

bit

eq;

if(!$cast(tr, rhs)) `uvm_fatal("transl", "ILLEGAL do_compare() cast")

eq = super.do_compare(rhs, comparer);

eq &= (dout === tr.dout);

return(eq);

endfunction

function string input2string();

return($sformatf("din=%4h rst_n=%b", din, rst_n));

endfunction

function string output2string();

return($sformatf("dout=%4h", dout));

endfunction

function string convert2string();

return($sformatf({input2string(), " ", output2string()}));

endfunction

endclass

```

```

Figure 27 - trans1 example with do_copy() and do_compare() methods defined

```

# 8.7. print(), sprint() and do\_print()

The built-in print() method is a void function that prints all of the field-macro defined fields in a table format by default. A print() method would only print the table header and footer if field macros are omitted and do\_print() is not overridden by the user. Printing with the print() method is not tracked in the final UVM Report Summary because it cannot be called from the message macros with "id" string fields. Because the print() method is not called from the message macros, it also cannot be suppressed by using different UVM verbosity settings.

By contrast, the built-in **sprint()** method is a function that returns a multi-line formatted string with all of the defined fields in a table format (by default) and should be called from the message macros. Printing with the **sprint()** method *is* tracked in the final UVM Report Summary and since it is called from the message macros, it can be suppressed by using different UVM verbosity settings.

Since it is very likely that some user will attempt to call the transaction print() method, the next two either-or guidelines are recommended to avoid unexpected results.

Guideline: Implement the print() method using field macros. -OR-

Guideline: Implement a do\_print() method that returns the following string, "print() and sprint() are not implemented for this transaction type" as shown in Figure 28.

More important guidelines regarding transaction printing are shown below.

Guideline: Avoid using the print() method. Its output is verbose and cannot be suppressed by using UVM verbosity settings.

Guideline: Avoid using the **sprint()** method. Its output is verbose.

Guideline: If you do use one of the built-in printing methods, choose sprint() over print() and call it from a UVM message macro. Runtime verbosity settings can mask verbose sprint() method printouts if desired.

Guideline: Define and use the convert2string() method discussed in earlier sections. convert2string() is more simulation efficient, more print-space efficient and can be easily suppressed by using different runtime UVM verbosity settings.

The built-in print() and sprint() methods either implement the required code as defined by the field macros or they call the built-in do\_print() virtual function. The built-in do\_print() virtual function, as defined in uvm\_object, is an empty method, so if field macros are used to define the fields of the transaction class, the built-in print() and sprint() methods will be populated with the proper printing code from most field macros and then they will execute the empty do\_print() method, which will perform no additional activity.

The default do\_print() method defined in the uvm\_object virtual base class is empty. The relevant code snippets are shown in Figure 29.

```

extern virtual function void do_print(uvm_printer printer);

...

function void uvm_object::do_print(uvm_printer printer);

return;

endfunction

```

$Figure \ 29 \ \text{-} \ do\_print() \ inherited \ virtual \ method \ prototype \ and \ source \ code$

#### 8.8. record() and do\_record()

The built-in **record()** method executes the \_\_m\_uvm\_field\_automation() method with the required record code as defined by the field macros (if used) and calls the built-in **do\_record()** virtual function. The built-in **do\_record()** virtual function, as defined in the **uvm\_object** base class, is also an empty method, so if field macros are used to define the fields of the transaction, the built-in **record()** method will be populated with the proper code to record the transaction fields from the field macro definitions and then it will execute the empty **do\_record()** method which will perform no additional activity.

The default do\_record() method defined in the uvm\_object virtual base class is empty. The relevant code snippets are shown in Figure 30.

```

extern virtual function void do_record (uvm_recorder recorder);

...

function void uvm_object::do_record(uvm_recorder recorder);

return;

endfunction

```

$Figure \ 30 \ \text{--} \ do\_record() \ inherited \ virtual \ method \ prototype \ and \ source \ code$

## 8.9. pack() and do\_pack()

The built-in pack(), pack\_bytes(), and pack\_ints() methods execute the \_\_m\_uvm\_field\_automation() method with the required packing code as defined by the field macros (if used) and then

they call the built-in do\_pack() virtual function. The built-in do\_pack() virtual function, as defined in the uvm\_object base class, is an empty method, so if field macros are used to define the fields of the transaction class, the built-in pack(), pack\_bytes(), and pack\_ints() methods will be populated with the proper packing code from most field macro definitions and then they will execute the empty do\_pack() method which, will perform no additional activity.

The default do\_pack() method defined in the uvm\_object virtual base class is empty. The relevant code snippets are shown in Figure 31.

```

extern virtual function void do_pack (uvm_packer packer);

...

function void uvm_object::do_pack (uvm_packer packer );

return;

endfunction

```

$Figure \ \textbf{31-do\_pack}() \ inherited \ virtual \ method \ prototype \ and \ source \ code$

## 8.10. unpack() and do\_unpack()

Similarly, the built-in unpack(), unpack\_bytes(), and unpack\_ints() methods execute the \_\_m\_uvm\_field\_automation() method with the required unpacking code as defined by the field

```

SNUG 2014

Rev 1.1

```

macros (if used) and then they call the built-in do\_unpack() virtual function. The built-in do\_unpack() virtual function, as defined in the uvm\_object base class, is an empty method, so if field macros are used to define the fields of the transaction class, the built-in unpack(), unpack\_bytes(), and unpack\_ints() methods will be populated with the proper unpacking code from most field macro definitions and then they will execute the empty do\_unpack() method, which will perform no additional activity.

The default do\_unpack() method defined in the uvm\_object virtual base class is empty. The relevant code snippets are shown in Figure 32.

```

extern virtual function void do_unpack (uvm_packer packer);

...

function void uvm_object::do_unpack (uvm_packer packer);

return;

endfunction

```