World Class SystemVerilog & UVM Training

# Finite State Machine (FSM) Design & Synthesis using SystemVerilog - Part I

Clifford E. Cummings

**Heath Chambers**

Sunburst Design, Inc. Provo, UT, USA HMC Design Verification, Inc. Albuquerque, NM, USA

www.sunburst-design.com

#### ABSTRACT

There are at least seven different Finite State Machine (FSM) design techniques that are commonly taught, one with combinatorial outputs and six with registered outputs. This paper will describe four of the FSM design techniques: (1) 1-Always Block Style with registered outputs, (2) 2-Always Block Style with combinatorial outputs, (3) 3-Always Block Style with registered outputs, and (4) 4-Always Block Style with registered outputs

This paper establishes measurement techniques to determine good coding styles and also shows synthesis results for ASIC designs.

Multiple benchmark FSM designs are used to measure coding style and synthesis efficiency.

The other three FSM design styles will be described in follow-on papers.

# **Table of Contents**

| Finite State Machine (FSM) Design & Synthesis using SystemVerilog - Part I     | 1  |

|--------------------------------------------------------------------------------|----|

| 1. Introduction                                                                | 6  |

| 2. Important design goals                                                      | 7  |

| 2.1 More code = more bugs                                                      | 7  |

| 3. FSM Coding Style Metrics                                                    | 8  |

| 4. State machine types                                                         | 8  |

| 4.1 Moore -vs- Mealy                                                           | 8  |

| 4.2 Binary -vs- OneHot encoding                                                | 9  |

| 5. ASIC -vs- FPGA Synthesis                                                    | 9  |

| 6. SystemVerilog FSM coding styles                                             | 10 |

| 6.1 One Always Block FSM coding style - registered outputs                     | 10 |

| 6.2 Two Always Block FSM coding style - combinatorial outputs                  | 10 |

| 6.3 Three Always Block FSM coding style - registered outputs                   | 11 |

| 6.4 Four Always Block FSM coding style - registered outputs                    | 12 |

| 7. SystemVerilog FSM Coding Tips & Tricks                                      | 13 |

| 7.1 Logic data type                                                            | 13 |

| 7.2 Assignments using '0 / '1 / 'x -vs- 1'b0 / 1'b1 / 1'bx                     | 13 |

| 7.3 FSM module header & port list                                              | 15 |

| 7.4 Enumerated state types                                                     | 15 |

| 7.5 FMS RTL code should use SystemVerilog always_ff and always_comb procedures | 17 |

| 7.6 FSM State Register                                                         | 17 |

| 7.7 Default next='x -vs- default next=state                                    | 18 |

| 7.8 Next state naming convention                                               | 19 |

| 7.9 Next assignments placed in a column                                        | 20 |

| 7.10 Loopback next state assignments                                           | 21 |

| 7.11 Default output assignments                                                | 21 |

| 7.12 Nonblocking Assignment race conditions?                                   | 22 |

| 8. Benchmark FSM designs                                                       | 23 |

| 8.1 FSM1 with 4 states, 2 outputs and 2 inputs                                 | 25 |

| 8.2 FSM7 with 10 states, 1 output and 2 inputs                                 | 27 |

| 8.3 FSM8 with 10 states, 3 outputs and 2 inputs                                | 33 |

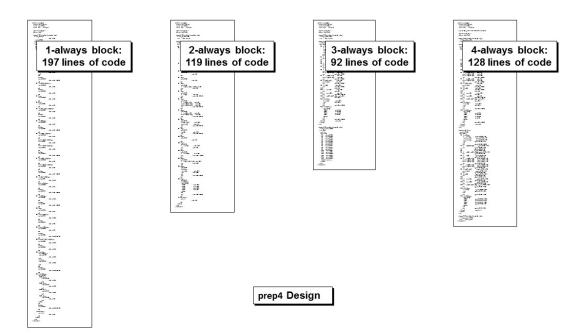

| 8.4 Prep4 FSM design with 16 states, 8-bit output and 8-bit input              | 35 |

| 9. Comparisons & Summary                                                       | 38 |

| 10. Acknowledgem   | ents                                                                 | 39 |

|--------------------|----------------------------------------------------------------------|----|

| 11. References     |                                                                      | 39 |

| 12. Author & Conta | ct Information                                                       | 41 |

| Appendix 1 Tools   | s and OS versions                                                    |    |

| Appendix 2 FSM     | benchmark source code                                                | 43 |

| Appendix 2.1       | FSM1 - fsm1_pkgs for abstract and binary encoded enums               | 43 |

| Appendix 2.2       | FSM1 - 1 always block RTL - NOT Recommended - Registered Outputs     | 44 |

| Appendix 2.3       | FSM1 - 2 always block RTL - Recommended - Combinatorial Outputs      | 45 |

| Appendix 2.4       | FSM1 - 3 always block RTL- NOT Recommended - Registered Outputs      | 46 |

| Appendix 2.5       | FSM1 - 4 always block RTL - Recommended - Registered Outputs         | 47 |

| Appendix 2.6       | FSM7 - fsm7_pkgs for abstract and binary encoded enums               | 48 |

| Appendix 2.7       | FSM7 - 1 always block RTL - NOT Recommended - Registered Outputs     | 49 |

| Appendix 2.8       | FSM7 - 2 always block RTL - Recommended - Combinatorial Outputs      | 51 |

| Appendix 2.9       | FSM7 - 3 always block - Recommended - Registered Outputs             | 52 |

| Appendix 2.1       | ) FSM7 - 4 always block RTL - Recommended - Registered Outputs       | 53 |

| Appendix 2.1       | 1 FSM8 - fsm8_pkgs for abstract and binary encoded enums             | 55 |

| Appendix 2.12      | 2 FSM8 - 1 always block RTL - NOT Recommended - Registered Outputs   | 56 |

| Appendix 2.13      | 3 FSM8 - 2 always block RTL - Recommended - Combinatorial Outputs    | 59 |

| Appendix 2.14      | FSM8 - 3 always block - Recommended - Registered Outputs             | 61 |

| Appendix 2.1       | 5 FSM8 - 4 always block RTL - Recommended - Registered Outputs       | 63 |

| Appendix 2.1       | 6 PREP4 - prep4_pkgs for abstract and binary encoded enums           | 65 |

| Appendix 2.1       | 7 PREP4 - 1 always block RTL - NOT Recommended - Registered Outputs. | 66 |

| Appendix 2.18      | B PREP4 - 2 always block RTL - Recommended - Combinatorial Outputs   | 70 |

| Appendix 2.19      | 9 PREP4 - 3 always block - Recommended - Registered Outputs          | 73 |

| Appendix 2.20      | ) PREP4 - 4 always block RTL - Recommended - Registered Outputs      | 75 |

# Table of Figures

| Figure 1 - Moore & Mealy State Machine block diagram     | 8  |

|----------------------------------------------------------|----|

| Figure 2 - Binary -vs- OneHot state diagrams             | 9  |

| Figure 3 - Block diagram for 1-always block coding style | 10 |

| Figure 4 - Block diagram for 2-always block coding style | 11 |

| Figure 5 - Block diagram for 3-always block coding style | 11 |

| Figure 6 - Block diagram for 4-always block coding style | 12 |

| Figure 7 - FSM1 state diagram - used for example code    | 13 |

| Figure 8 - DesignVision error messages from bad usage of always_ff begin-end statemer | ıts18 |

|---------------------------------------------------------------------------------------|-------|

| Figure 9 - FSM loopback state assignment styles                                       | 21    |

| Figure 10 - FSM1 state diagram                                                        | 25    |

| Figure 11 - fsm1 - Coding styles effort comparison                                    | 25    |

| Figure 12 - fsm1 - Lines of code                                                      |       |

| Figure 13 - fsm1 - Coding goals summary                                               |       |

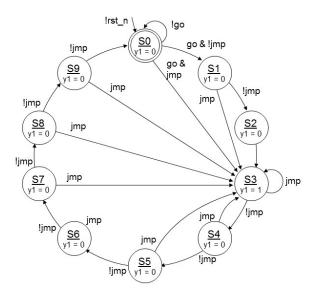

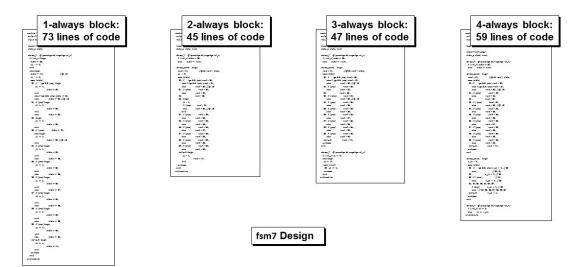

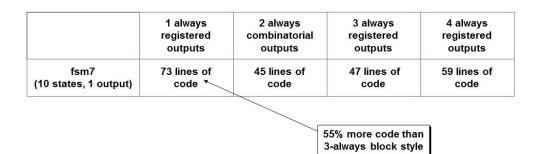

| Figure 14 - FSM7 state diagram                                                        |       |

| Figure 15 - fsm7 - Coding styles effort comparison                                    |       |

| Figure 16 - fsm7 - Lines of code                                                      |       |

| Figure 17 - fsm7 - Coding goals summary                                               |       |

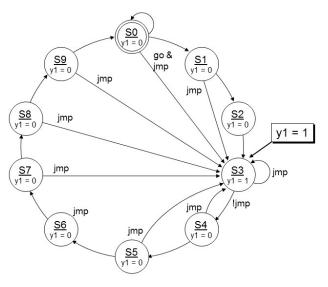

| Figure 18 - FSM7 state diagram - why is the 1-always block style so verbose?          |       |

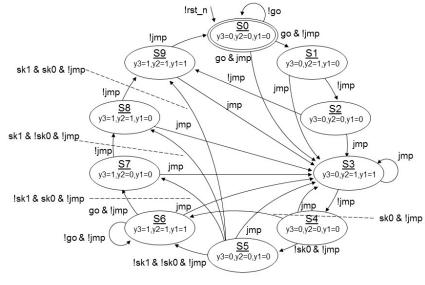

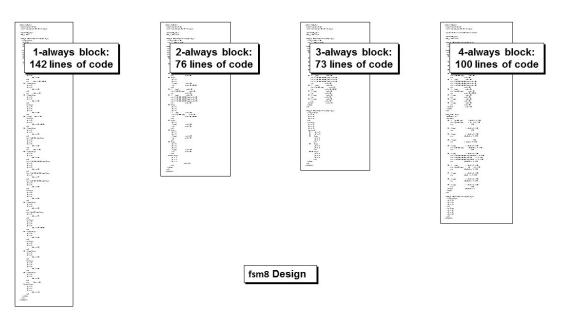

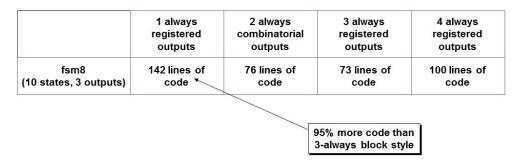

| Figure 19 - FSM8 state diagram                                                        |       |

| Figure 20 - fsm8 - Coding styles effort comparison                                    |       |

| Figure 21 - fsm8 - Lines of code                                                      |       |

| Figure 22 - fsm8 - Coding goals summary                                               |       |

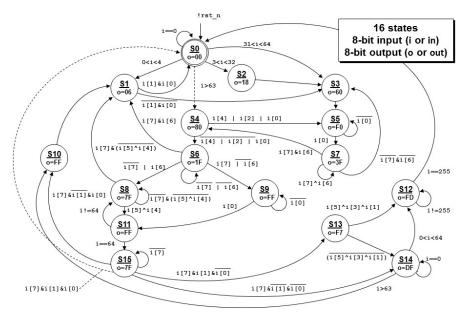

| Figure 23 - Prep4 state diagram                                                       |       |

| Figure 24 - prep4 - Coding styles effort comparison                                   |       |

| Figure 25 - prep4 - Lines of code                                                     |       |

| Figure 26 - prep4 - Coding goals summary                                              |       |

# Table of Examples

| Example 1 - FSM1 module header and port list example15                                      |

|---------------------------------------------------------------------------------------------|

| Example 2 - FSM1: fsm1_pkg_a.sv with abstract enumerated state_e typedef16                  |

| Example 3 - FSM1: fs1_pkg_b.sv encoded state_e typedef w/logic data type and bit-range16    |

| Example 4 - FSM1: importing fsm1_pkg::*; (abstract or binary) with state/next declaration16 |

| Example 5 - FSM state register declaration17                                                |

| Example 6 - Bad usage of always_ff begin-end statements                                     |

| Example 7 - Default next='x combinatorial always_comb procedure for FSM designs             |

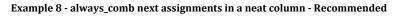

| Example 8 - always_comb next assignments in a neat column - Recommended                     |

| Example 9 - always_comb next assignments following contour of the code - NOT Recommended 20 |

| Example 10 - FSM registered output assignments using an always_ff procedure                 |

| Example 11 - fsm7_1 - 1-always block style output assignments for each transition arc       |

| Example 12 - File: fsm1_pkg_a.sv - fsm1_pkg enumerated typedef43                            |

| Example 13 - File: fsm1_pkg_b.sv - fsm1_pkg enumerated typedef43                            |

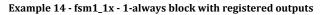

| Example 14 - fsm1_1x - 1-always block with registered outputs           | 44 |

|-------------------------------------------------------------------------|----|

| Example 15 - fsm1_2x - 2-always block with combinatorial outputs        | 45 |

| Example 16 - fsm1_3x - 3-always block style with registered outputs     | 46 |

| Example 17 - fsm1_4x - 3-always block style with registered outputs     | 47 |

| Example 18 - File: fsm7_pkg_a.sv - fsm7_pkg enumerated typedef          | 48 |

| Example 19 - File: fsm7_pkg_b.sv - fsm7_pkg enumerated typedef          | 48 |

| Example 20 - fsm7_1x - 1-always block style with registered outputs     | 50 |

| Example 21 - fsm7_2x - 2-always block style with combinatorial outputs  | 51 |

| Example 22 - fsm7_3x - 3-always block style with registered outputs     | 52 |

| Example 23 - fsm7_4x - 4-always block style with registered outputs     | 54 |

| Example 24 - File: fsm8_pkg_a.sv - fsm8_pkg enumerated typedef          | 55 |

| Example 25 - File: fsm8_pkg_b.sv - fsm8_pkg enumerated typedef          | 55 |

| Example 26 - fsm8_1x - 1-always block style with registered outputs     | 58 |

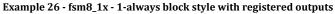

| Example 27 - fsm8_2x - 2-always block style with combinatorial outputs  | 60 |

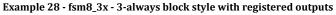

| Example 28 - fsm8_3x - 3-always block style with registered outputs     | 62 |

| Example 29 - fsm8_4x - 4-always block style with registered outputs     | 64 |

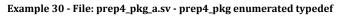

| Example 30 - File: prep4_pkg_a.sv - prep4_pkg enumerated typedef        | 65 |

| Example 31 - File: prep4_pkg_b.sv - prep4_pkg enumerated typedef        | 65 |

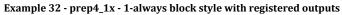

| Example 32 - prep4_1x - 1-always block style with registered outputs    | 69 |

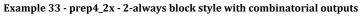

| Example 33 - prep4_2x - 2-always block style with combinatorial outputs | 72 |

| Example 34 - prep4_3x - 3-always block style with registered outputs    | 74 |

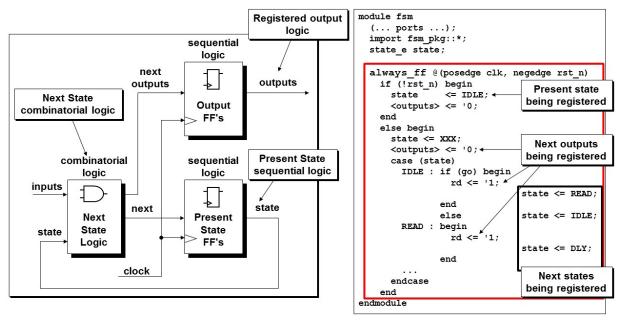

| Example 35 - prep4_4x - 4-always block style with registered outputs    | 77 |

### **Table of Tables**

| Table 1 - Average time verification engineers spend in various tasks | 7  |

|----------------------------------------------------------------------|----|

| Table 2 - fsm1 - Synthesis efficiency comparison table               | 26 |

| Table 3 - fsm7 - Synthesis efficiency comparison table               | 29 |

| Table 4 - fsm8 - Synthesis efficiency comparison table               | 34 |

| Table 5 - prep4 - Synthesis efficiency comparison table              | 36 |

### 1. Introduction

What could possibly be new about Finite State Machine (FSM) design? Hasn't this topic been completely covered by existing publications?

Sunburst Design has been teaching six different FSM coding styles, plus a few minor variants, for more than two decades and the last paper that Cliff did on this topic was presented in 2003. Cliff & Heath have made many new observations and refinements to the FSM coding techniques and we have observed synthesis improvements using FSM coding styles. Also, FSM synthesis can have interesting differences when synthesizing for ASICs and FPGAs. This paper shares fundamental FSM coding styles along with newer FSM design techniques that we have refined in the 15 years since Cliff's last FSM conference paper.

FSM design is actually a very large topic. The seven major FSM coding styles include one FSM coding style with combinatorial outputs and six FSM coding styles with registered outputs. Registering module outputs is typically recommended by synthesis tool vendors as it helps meet timing goals more easily without using multiple different input and output timing design constraints. Registered outputs are also glitch-free. There is nothing inherently wrong with FSM combinatorial outputs when glitching outputs are used internally to an ASIC or FPGA design and settle before the next active clock edge to meet register setup times, which can be proven with Static Timing Analysis (STA) tools, so we do show one reasonable FSM coding style with combinatorial outputs.

Heath and Cliff generally recommend doing FSM design with registered outputs and there are multiple FSM coding styles that achieve that goal.

The seven different coding styles that we commonly teach are:

- 2-always block coding style with combinatorial outputs.

- 1-always block coding style with registered outputs.

- 3-always block coding style with registered outputs.

- 4-always block coding style with registered outputs (new style not previously shown).

- Indexed OneHot coding style with registered outputs.

- Parameter OneHot coding style with registered outputs.

- Output encoded coding style with registered outputs.

This topic is large enough that it is our intent to break documentation on these styles into three papers with this being the first. This paper will cover the first four coding styles listed above with the remaining three coding styles and sub-variations to be covered in subsequent papers.

In the process of writing this paper, we discovered that the 1-always block coding style typically infers a design that is somewhat smaller and faster than our preferred 3-always block coding style. We found that creating a 4-always block FSM design could achieve the same synthesis results as the 1-always block style while still being a much more concise coding style than the 1-always block style. The reasons for these claims and the 4-always block coding style are included in this paper.

## 2. Important design goals

Harry Foster of Mentor, A Siemens Business, has conducted industry trend studies using the Wilson Research Group, which we believe are the best and most reliable studies in our industry. These studies have shown design and verification trends for ASIC & FPGA design since the year 2010. In the year 2010, Cliff Cummings and Harry Foster conducted Assertion Based Verification seminars worldwide and in those seminars, Harry consistently claimed that the activity that was most responsible for putting a project behind schedule was debug time.

| 2010                         | 2012                                                | 2014-FPGA                                                                                                          | 2014-ASIC                                                                                                                                                                                   | 2016-FPGA                                                                                                                                                                                                                                                      | 2016-ASIC                                                                                                                                                                                                                                                                                                                                         | 2018-FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37%                          | 36%                                                 | 43%                                                                                                                | 37%                                                                                                                                                                                         | 43%                                                                                                                                                                                                                                                            | 39%                                                                                                                                                                                                                                                                                                                                               | 42%                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 27%                          | 23%                                                 | 19%                                                                                                                | 24%                                                                                                                                                                                         | 21%                                                                                                                                                                                                                                                            | 22%                                                                                                                                                                                                                                                                                                                                               | 19%                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| estbench Development 28% 22% |                                                     | 20%                                                                                                                | 22%                                                                                                                                                                                         | 20%                                                                                                                                                                                                                                                            | 22%                                                                                                                                                                                                                                                                                                                                               | 20%                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 14%                          | 20%                                                 | 17%                                                                                                                | 17%                                                                                                                                                                                         | 16%                                                                                                                                                                                                                                                            | 17%                                                                                                                                                                                                                                                                                                                                               | 18%                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| numbers do<br>n to 100%      | un Ctudios                                          | Sin                                                                                                                |                                                                                                                                                                                             | 00 0                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                   | ore                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                              | 37%<br>27%<br>28%<br>14%<br>numbers do<br>n to 100% | 37%         36%           27%         23%           28%         22%           14%         20%           numbers do | 37%         36%         43%           27%         23%         19%           28%         22%         20%           14%         20%         17%           numbers do<br>n to 100%         Sin | 37%         36%         43%         37%           27%         23%         19%         24%           28%         22%         20%         22%           14%         20%         17%         17%           numbers do no 100%         Since 2014, Deb effort than | 37%         36%         43%         37%         43%           27%         23%         19%         24%         21%           28%         22%         20%         22%         20%           14%         20%         17%         17%         16%           numbers do<br>n to 100%         Since 2014, Debugging has ta<br>effort than any other sin | 37%         36%         43%         37%         43%         39%           27%         23%         19%         24%         21%         22%           28%         22%         20%         22%         20%         22%           14%         20%         17%         17%         16%         17%           numbers do no 100%         Since 2014, Debugging has taken ~95% m effort than any other single activity         20%         20%         20% |

Table 1 - Average time verification engineers spend in various tasks

The Wilson Research Group Studies from 2010[6], 2012[7], 2014[8][9], 2016[10][11] and 2018[12] all showed that debug time consistently consumed the most verification engineering time. Since 2014 as shown in Table 1, debugging has taken on average  $\sim$ 95% more effort than any other verification task.

It is clear from these studies that any coding habit that helps to minimize debug time is an important habit to develop. The RTL coding guidelines shared in this paper help to reduce debug time.

#### 2.1 More code = more bugs

It has often been said that more lines of code equals more bugs. A quick online search could not find definitive sources for this claim but in all of the sources referenced, none made the counter claim and many sources gave reasoned arguments why the claim that more\_lines = more\_bugs makes sense [19][20][21][22][23][24][25][26].

For these reasons, we believe that *concise coding styles* that follow *defensive coding guidelines to either avoid bugs* or to enable early detection are of greatest value in RTL design in general and FSM design in particular. Throughout this paper we will emphasize where we have used concise coding styles and styles that help to easily identify bugs.

### **3. FSM Coding Style Metrics**

In order to judge what makes a good coding style, we selected the following goals that can be used to judge the various coding styles:

- 1. The FSM coding style should be *easily modifiable to change state encodings and FSM styles.*

- 2. The coding style should be *concise*.

- 3. The coding style should be *easy to code and understand*.

- 4. The coding style should help *facilitate debugging*

- 5. The coding style should *yield efficient synthesis results*

- 6. The coding style should be *easy to change due to FSM modifications* including modifying the number of inputs and outputs.

These metrics will be evaluated for each coding style and tabulated at the end of this paper.

### 4. State machine types

There are two principle state machine classifications that apply to all state machine designs.

#### 4.1 Moore -vs- Mealy

A Moore state machine is classified as an FSM where the outputs are only a function of the present state, while Mealy state machines have one or more outputs that are a function of the present state and one or more FSM inputs.

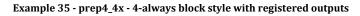

Figure 1 - Moore & Mealy State Machine block diagram

Moore state machines are favored in industry because the outputs have a full cycle to settle through the combinatorial logic and are therefore easier to meet required cycle times. Mealy outputs allow an input to appear after the cycle has started, and the input must still traverse the combinatorial logic and meet setup time for the Mealy output. If the design absolutely requires an input to make it onchip after the active clock edge, pass through logic and appear on the output all within one cycle, those are the designs that typically use a Mealy output.

Using a play on words, it is said that, "Moore is Less" meaning that Moore state machines are only dependent on the current state while Mealy State Machines are dependent on the current state and one or more inputs.

In general, we avoid Mealy FSM designs unless absolutely necessary.

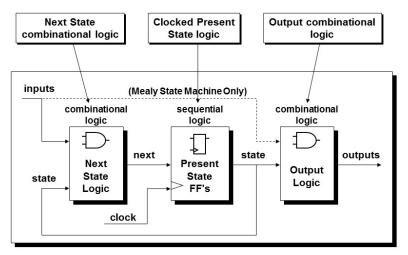

#### 4.2 Binary -vs- OneHot encoding

The second major classification is whether the state encoding of the FSM designs are binary (also referred to as highly encoded) or if they are OneHot.

There are multiple binary encoded styles but what they have in common is that they typically use fewer flip-flops to create unique binary encodings for each state in the FSM design than OneHot FSM designs.

OneHot encoding uses one flip-flop for each state in the state machine and when the state machine is in that state, that flip-flop is "hot" or equal to "1" while the rest of the states are equal to "0." Since transitioning from one state to another only requires that the previous hot flip-flop be set to 0 and the new hot flip-flop be set to 1, the combinatorial logic to transition between states is typically very simple. As will be explained in Section 5. OneHot FSM designs are typically inferred automatically by FPGA synthesis tools.

Figure 2 - Binary -vs- OneHot state diagrams

## 5. ASIC -vs- FPGA Synthesis

There are two important differences between ASIC & FPGA design.

For ASICs, the general rule is that "silicon is free and flip-flops cost." Adding another nand gate to a combinatorial path typically does not add much delay to the path, but every flip-flop adds blocks of clocked logic, which do consume space.

For FPGAs, the general rule is that "flip-flops are free and combinatorial logic costs." FPGAs typically have more flip-flops than are needed for most designs so using the extra flip-flops does not add more silicon to the design, while the speed of an FPGA is largely determined by the size of the combinatorial logic. If the combinatorial logic fits into one Look Up Table (LUT) the logic is fast. If the combinatorial logic requires two LUTs to implement the combinatorial function, then there is one lookup delay, one or more trace delays, and a second lookup delay, which typically causes the combinatorial logic delay to be more than twice as long as a one-LUT combinatorial implementation.

Since OneHot FSM designs typically require smaller combinatorial logic (as discussed in Section 4.2 ), FPGA synthesis tools synthesize OneHot State Machines for smaller FSM designs by default, regardless of the state encoding included in the RTL code. For this reason, FPGA synthesis tools are sometimes more forgiving when it comes to optimizing synthesis coding styles. As long as the FPGA synthesis tool recognizes that the RTL code will infer an FSM, the synthesis tool creates a very good OneHot FSM design and largely ignores the coding style used by the RTL designer.

FPGA synthesis tools frequently have a special setting (typically a GUI switch) to turn off the automatic creation of OneHot FSM designs. OneHot FPGA designs will be described in the Part II FSM paper.

### 6. SystemVerilog FSM coding styles

The four FSM coding styles discussed in this paper are the 1-always block with registered outputs, 2always block with combinatorial outputs, 3-always block with registered outputs and 4-always block with registered outputs. OneHot and Output Encoded FSM coding styles will be discussed in subsequent publications.

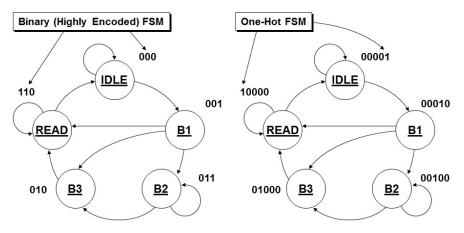

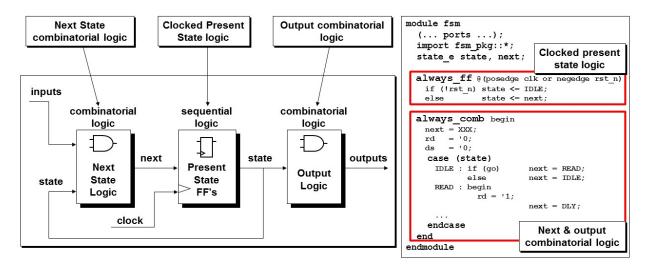

#### 6.1 One Always Block FSM coding style - registered outputs

The 1-always block FSM coding style can be viewed as a single <code>always\_ff</code> procedure (shown in Figure 3) that handles the state register, the next <code>state</code> assignments and the outputs that belong to the next <code>state</code> for each transition arc. The trick used in this coding style is to recognize that the output assignments are for the state you are going to next and not for the current state being tested in the <code>case</code> statement. The 1-always block coding style requires designers to set the outputs for each transition arc to that <code>state</code> and not just once for that <code>state</code>. This is why this coding style is so verbose. On the positive side, the synthesis results are typically better than the 2-always block and 3-always block coding styles since the next <code>state</code> and next-outputs are being generated in parallel in the single <code>always\_ff</code> procedure. The fix for the 3-always block synthesis inefficiency is to split the final <code>always\_ff</code> procedure, thus creating the 4-always block coding style as shown in section 6.4.

Figure 3 - Block diagram for 1-always block coding style

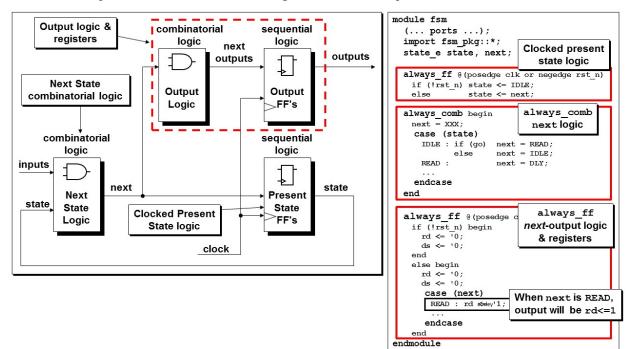

### 6.2 Two Always Block FSM coding style - combinatorial outputs

The 2-always block FSM coding style can be viewed as an **always\_ff** state register (just 3 lines of

code) followed by an **always\_comb** procedure to represent the combined **next** state logic and combinatorial output logic. Optionally, the outputs can be separated from the **always\_comb** procedure and placed into a separate **always\_comb** procedure or into one or more continuous assignment statements.

Figure 4 - Block diagram for 2-always block coding style

#### 6.3 Three Always Block FSM coding style - registered outputs

The 3-always block FSM coding style can be viewed as an **always\_ff** state register (just 3 lines of code) followed by an **always\_comb** procedure to represent the **next** state combinatorial logic and an **always\_ff** procedure to calculate and register the next outputs.

Figure 5 - Block diagram for 3-always block coding style

The trick used in this coding style is to recognize that the output assignments are the "next" output assignments and not the output assignments for the current state, so the final <code>always\_ff</code> procedure will use a **case** statement to test the **next** state, not the current state. Since the outputs are calculated from the **next** state logic, this can add extra logic when synthesized as the **next** state was already calculated from input conditions. This means that there is one block of combinatorial logic that calculates the **next** state and that feeds a second block of combinatorial logic to calculate the next outputs, which can create larger and slower combinatorial logic. In the 1-always block coding style, the inputs and **state** variables are used to calculate both the **next** state and next outputs in parallel, which can reduce the size and delay through the combinatorial next output logic. This inefficiency will be addressed in the 4-always block coding style described in the next section.

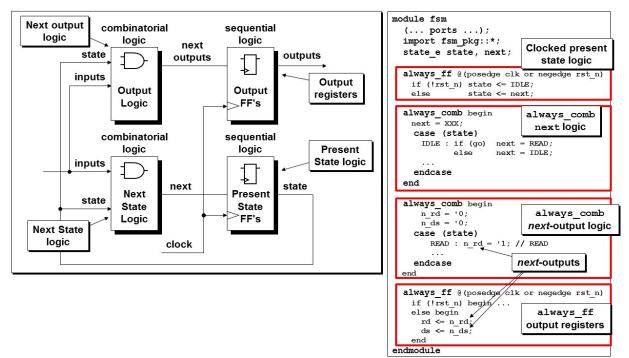

#### 6.4 Four Always Block FSM coding style - registered outputs

While writing this paper, we discovered that the 1-always block coding style required much more code but typically gave better synthesis results than the 3-always block coding style. This was a bit of a surprise until we realized that the next-output combinatorial logic of the 3-always block coding style is fed by another block of combinatorial logic that was used to calculate the **next** state. The 1-always block coding style generated the **next** state and next-outputs in parallel, in the same combinatorial block of logic.

We found that creating a 4-always block coding style where the combinatorial nextout values are created from an **always\_comb** procedure that simultaneously examines the registered state outputs along with the FSM inputs, would generally give the same optimized synthesis results as the 1-always block coding style with far fewer lines of code. The first **always\_ff** and **always\_comb** procedures are identical to the 3-always block coding style. The third **always\_ff** procedure from the 3-always block coding style is split into an **always\_comb** procedure to calculate the next-output logic and an **always\_ff** procedure to register the next-outputs. These optimizations improved synthesis results to match the results observed with the 1-always block style.

Figure 6 - Block diagram for 4-always block coding style

### 7. SystemVerilog FSM Coding Tips & Tricks

As of the year 2019 and after 15 years of SystemVerilog FSM coding, we have compiled some of our favorite FSM coding tips and tricks. You do not have to follow any of these tips and tricks to implement a working and synthesis-efficient FSM design, but we have found them to be useful and advantages of using each trick will be explained. Users are encouraged to implement their favorite tricks from this list and feel free to share back with us some of your favorite tricks.

Many of these tricks fall into the category of "less is better." We find it easier to visualize a design that is concise and where more of the design can be viewed without additional scrolling on a computer screen or flipping of printed pages. For us, a well formatted and concise design earns extra points.

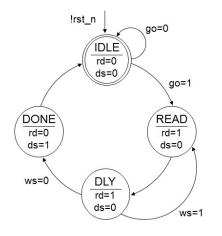

To help explain the tips & tricks, we will use the following very simple Moore state machine with four states, two inputs and two outputs.

Figure 7 - FSM1 state diagram - used for example code

#### 7.1 Logic data type

For SystemVerilog RTL coding, designers should follow this guideline:

Declare all data types to be of type *logic* unless there are multiple drivers on the signal, then use the *wire* data type.

The three most common sources for valid multi-driver-signal designs are bus crossbars, OneHot multiplexers and bidirectional buses, all of which are becoming increasingly scarce in modern hardware design. Any logic that includes three-state logic is strongly discouraged in contemporary ASIC designs and almost non-existent in modern FPGA designs.

The strong advantage of the **logic** data type is that if a designer ever mistakenly makes multiple assignments to the same signal, the simulation *compiler* will catch and report the error before an engineer ever simulates or synthesizes the design. Catching the error before simulation saves debug time.

**Checklist item:** Engineers should generally declare all FSM ports and all FSM internal signals to be of type logic.

### 7.2 Assignments using '0 / '1 / 'x -vs- 1'b0 / 1'b1 / 1'bx

SystemVerilog introduced a very convenient shorthand to assign all 0's, all 1's or all X's to a scalar signal or a vector bus. The notation is to assign '0 (all zeros), '1 (all ones) and 'x (all X's). Although

this is a small enhancement, it is useful for multiple reasons.

First, assigning '0 instead of 1'b0 is more concise, albeit by only two characters so this is not the compelling reason to use this style.

A better reason is that the notation 1'b0 is somewhat confusing and when the code is quickly scanned it is easy to mistake this assignment for a "1" while the shorter '0 conveys no such confusion.

So why not just use 0 or 1 to make an assignment? Assigning 0 or 1 is acceptable and common in Verilog designs and they typically work just fine, but assigning 0 is really assigning 32-bits of 0 while assigning 1 is really assigning 31-bits of 0 with LSB equal to 1 and Verilog quietly truncates the leading 31 bits when this is assigned to a 1-bit variable. This is fine unless the code is run through a linting tool, which frequently reports a warning that 32 bits are being assigned to a 1-bit variable. The assignment works fine but the warning is both annoying and distracting so engineers often add waivers to their linting tools to ignore this warning.

Coding '0 / '1 / 'x assigns as many 0's, 1's or X's as are required to fill the left-hand-side (LHS) variable or wire that is being assigned, so there is never any linting tool warning related to mismatched sizes when making these new SystemVerilog assignments.

Also when assigning X's using the older Verilog style, one must indicate how many X-bits are required for the assignment while 'x will fill the assigned variable with as many X's as are needed. This avoids bugs that might be introduced when widths are changed later in the design.

We use '0 / '1 / 'x for all of our FSM designs, and for that matter, for all of our SystemVerilog designs that do not require a non-repeated fill pattern. For more unusual assignment patterns, we still use the older Verilog style to indicate the bit-pattern and how many bits are required, for example 8'b0110\_1100 or 8'h6C.

**Checklist item:** Where ever possible, use the SystemVerilog '0 / '1 / 'x to make assignments.

#### 7.2.1 Caution using '0 / '1 / 'x

Although we recommend using these new assignment styles, there are two points of caution that engineers should understand.

First, assigning '1 will assign all 1's and not all 0's followed by a single 1. If you assign data[7:0]='1 then data will be equal to 8'hFF, not 8'hO1. '1 does indeed assign all 1's.

Second, when '0 / '1 / 'x are placed inside of concatenation, they are only 1-bit assignments and they do not fill the remaining bits with the pattern. If you assign data[7:0]={'1, 4'hA} the result will be that data is equal to 8'hIA and NOT 8'hFA. The reason that the '1 does not fill the leading bits is because what if multiple '1 / '0 assignments are included in the same concatenation? Where is the fill operation supposed to occur? Consider the following examples:

```

data[15:0] = {'1, 4'hA, '0};

// Which bits should be leading 1's and which bits should be trailing 0's?

data[15:0] = {'0, '1, '0};

// Which bits should be leading 1's, middle 0's and trailing 1's?

```

There were too many opportunities for confusion by adding '0 / '1 / 'x / 'z to concatenation, so the SystemVerilog Standards Group decided that when this shorthand notation was used in concatenation that the notation would only expand to a single bit each. In the above examples, the values expand as shown below.

```

data[15:0] = {'1, 4'hA, '0};

// is equal to 16'b0000_0000_0011_0100 or 16'h0034

data[15:0] = {'0, '1, '0};

// is equal to 16'b0000_0000_0000_0010 or 16'h0002

```

#### 7.3 FSM module header & port list

The FSM module header and port list should be coded using the Verilog-2001 concise port list style. All ports should be declared to be of type logic for the reasons discussed in Section 7.1 We order the port list as outputs followed by inputs followed by control inputs. The outputs-inputs order is not required by Verilog or SystemVerilog and many engineers prefer to list inputs followed by outputs. Since Verilog gate primitives can only be instantiated using positional ports and since the order is always outputs followed by inputs followed by control inputs, we follow that same convention with our own modules. We have also been told by engineering colleagues that most module changes are related to adding or modifying the inputs and that it is easier to modify the end of the list as opposed to the front or center of the list.

The module header and port list for the FSM1 design is shown in Example 1.

```

module fsm1_3 (

output logic rd, ds,

input logic go, ws, clk, rst_n);

```

Example 1 - FSM1 module header and port list example

Many engineers list each port on a separate line and there is nothing specifically wrong with that practice, but we prefer to group multiple signals into each **output** and **input** declaration as shown in Example 1, to reduce the number of lines of code in the FSM design and to allow more of the FSM design to be visible per page when examining the code.

**Checklist item:** Use the Verilog-2001 concise port declaration style and declare all ports to be of type logic. Extra points for listing outputs followed by inputs followed by control inputs. Extra points for grouping multiple signals into each output and input port list declaration.

#### 7.4 Enumerated state types

Enumerated types are used to make the **state** and **next** state declarations and then the enumerated state names are used throughout the FSM design.

While working on this paper, we discovered that there were multiple advantages to putting the enumerated declarations into a package as typedef[s] and then importing the package into the FSM design.

We used the naming convention of <fsm-name>\_pkg and we actually maintained two different FSM packages, one with abstract enumerated declaration typedef with filename <fsm-name>\_pkg\_a.sv ( \_a for abstract) and one with binary encoded enumerated declaration typedef with filename <fsm-name>\_pkg\_b.sv ( \_b for binary).

Using the FSM **enum typedef** packages offered the following advantages:

Each FSM coding style would import the same FSM packages and ensure that all the FSM styles used the exact same FSM typedef[s]. Fewer opportunities to make mistakes.

- (2) By maintaining pkg\_a and pkg\_b files, we could easily switch from abstract to binary encoded enum typedef[s] without maintaining two copies of each FSM file.

- (3) Simulation of either abstract or binary-encoded enum[s] was as easy as selecting and compiling the appropriate package before compiling the other simulation files since each package had the same identical package name. This gave us much easier code maintenance.

- (4) Similarly, synthesis of either abstract or binary-encoded enum[s] was as easy as compiling the appropriate package before compiling the other synthesis files since each package had the same identical package name. Again, much easier code maintenance.

- (5) If we wanted to try different enumerated assignments, we only had to change the pkg\_b file and all styles would use the exact same new encodings. We did not have to touch the FSM files themselves.

- (6) The testbench could easily use the same **state\_e typedef** to implement reference models to track expected FSM states, if desired.

- (7) The testbench could easily use **bind**-files for assertions or covergroups by using the **typedef** to input the **state** and **next** variables from the FSM design.

After we implemented the separate package files, we were able to cut the number of FSM benchmark files in half and ensured a more error-free coding style.

The enumerated declarations for the **state\_e typedef** can either be made using abstract state encodings as shown in

Example 2, or can be made using the logic data type, specifying the number of state bits as a range, and include user-defined encodings for each state as shown in Example 3.

endpackage

Example 2 - FSM1: fsm1\_pkg\_a.sv with abstract enumerated state\_e typedef

endpackage

Example 3 - FSM1: fs1\_pkg\_b.sv encoded state\_e typedef w/logic data type and bit-range

import fsml\_pkg::\*;

state\_e state, next;

Example 4 - FSM1: importing fsm1\_pkg::\*; (abstract or binary) with state/next declaration

It is typical for RTL coders to start with the abstract state and next declarations and to later add state encodings if desired. Since the state names are used throughout the FSM RTL code, adding state

encodings later does not require any additional RTL modifications to the FSM design.

The enumerated state names also show up automatically in a waveform display to help track state transitions and to help debug the state machine. It is often useful to show two copies of the enumerated names in the waveform display, the first showing the state names (which is the default mode for all waveform viewers) and the second copy with the radix changed to be binary, decimal or hex to see the state encodings (often useful for debugging). There is nothing in the IEEE SystemVerilog Standard[15] that requires a waveform viewer to show the state names by default, but all waveform viewers that we have used from all of the major EDA vendors show the state names by default.

It is a good practice to include an extra **xx** or **xxx** state in the list of declared state names as shown in both Example 2 and Example 3. This extra **xxx** state will be used to code the **always\_comb** procedure and this practice can help quickly debug an FSM design, plus if one chooses to include state encodings, the **xxx** state will be set to all X's, which are treated as "don't cares" by the synthesis tool to help optimize the synthesized design.

**Checklist item:** Declare the **state** and **next** variables using enumerated types. Add an **xx** or **xxx** state to help debug the design and to help optimize the synthesized result.

#### 7.5 FMS RTL code should use SystemVerilog always\_ff and always\_comb procedures

The RTL code for the FSM design should use **always\_ff** and **always\_comb** procedures to infer clocked and combinatorial logic. Do not use the older Verilog **always** procedures. The **always\_ff** and **always\_comb** procedures show designer intent and include built-in checking for bad RTL coding styles as described in the paper "SystemVerilog Logic Specific Processes for Synthesis - Benefits and Proper Usage[3]."

**Checklist item:** Use **always\_ff** and **always\_comb** procedures to infer clocked and combinatorial logic. Do not use the older Verilog **always** procedures.

#### 7.6 FSM State Register

The state register should be an **always\_ff** procedure and should be 3 lines of code, not 5 lines and not 6 lines. This state register is placed at the top of the FSM design, immediately following the FSM declarations, and requires no comment to note the obvious state register code. Since the state register code is at the top of the module, there is no need to search the remainder of the FSM design to see that the state register code was added and implemented properly.

With a **posedge clk** and a low-true asynchronous reset, our state registers are almost always exactly the following three lines of code:

```

always_ff @(posedge clk, negedge rst_n)

if (!rst_n) state <= IDLE;

else state <= next;</pre>

```

Example 5 - FSM state register declaration

There is no need to put the *if*-statement and the *state* assignment on separate lines and there is no need to put *begin* - *end* on the *always\_ff* procedure. Also, we place the reset state assignment and *next* state assignment into a nice, neat column for easy scanning and reading.

Note that adding **begin** - **end** to the **always\_ff** procedure is not only unnecessary, but introduces the opportunity to add code before the first **if** (!rst\_n) statement, which violates coding

requirements for some synthesis tools including Design Compiler. In short, the **always\_ff begin** - **end** allows an RTL designer to code and simulate something that might not be synthesizable and as such, we consider this to be a poor coding practice.

Consider the legal RTL code in Example 6.

Example 6 - Bad usage of always\_ff begin-end statements

This example code is legal SystemVerilog code and will simulate without error, but once this design is read into the DesignVision GUI, the following error messages are reported in a pop-up window:

```

1: Error:

<filename><line number>:

The statements in this 'always' block are outside the scope of the

synthesis policy. Only an 'if' statement is allowed at the top level in

this always block. (ELAB-302)

2: Error: Cant' read 'sverilog' file

<filename>

(UID-59)

```

Figure 8 - DesignVision error messages from bad usage of always\_ff begin-end statements

In short, the **begin** - **end** is unnecessary, needlessly verbose and introduces the opportunity to add bad code that might not be discovered until the design is read for synthesis.

**Checklist item:** Declare the state register using just 3 lines of code and place it at the top of the design after the enumerated type declaration.

#### 7.7 Default next='x -vs- default next=state

There are two common ways to code the always\_comb procedure for an FSM design. The two methods are to either make a pre-default-X next assignment or use a pre-default next=state assignment[16] with implied loopback assignments. While running synthesis benchmarks on both styles, and to our surprise, we discovered that the next='x pre-default-X assignment consistently gave better synthesis results over the pre-default next=state assignment style. The reason seems to be that the pre-default-X tends to fill out a synthesis-equivalent of the Karnaugh Map (K-Map) with X's, especially when there are fewer than 2<sup>n</sup> states in the FSM design. Even when adding case-default-X assignments to both styles, the pre-default-X assignment style consistently gave better synthesis results.

```

always_comb begin

next = XXX; // Pre-default-X assignment

case (state)

IDLE : if (go) next = READ;

else next = IDLE; //@ loopback

READ : next = DLY;

DLY : if (!ws) next = DONE;

else next = READ;

```

```

DONE : next = IDLE;

default: next = XXX; // case-default-X assignment

endcase

end

```

Example 7 - Default next='x combinatorial always\_comb procedure for FSM designs

Anyone who has done extensive RTL coding and simulation recognizes that, when it comes to RTL debugging, catastrophic RTL coding failures are the easiest to find, identify and fix. Conversely, subtle RTL coding errors can often be very time consuming to find and frequently require the RTL coder to add numerous debug printing messages to finally discover the subtle problem in the code. Making X-assignments can help cause catastrophic simulation failures when there is an RTL design problem, while implied loopback errors can often allow an FSM design to appear to be working for multiple clock cycles before the simulation reports an FSM simulation error.

So how does this work and what procedure do we recommend?

We strongly encourage engineers to make the pre-default **next='x** assignment in the FSM design. The pre-default X-assignments have two RTL simulation debug advantages and one RTL synthesis advantage.

The RTL simulation advantage is that assigning X's frequently causes the simulation to fail catastrophically if there is a missing **next** assignment. At the point where there is a missing **next** assignment, we say that the waveform display "starts to bleed red!" Wherever the **next** state assignment is missing, the waveform display will show that **next** is all X's and that is typically the exact point where the **next**-assignment is missing. This is a catastrophic simulation error that quickly identifies the missing assignment and, from our experience, is fixed very quickly.

The second RTL simulation advantage is that making a pre-default-X assignment requires the RTL coder to code an equation for each transition arc *from* each state. After completing the FSM design, a designer can double-check the code by counting the number of transition equations for each state in the RTL code and match that to the number of transition arcs in the state diagram. There is a one-to-one correspondence between the number of transition equations and transition arcs. Using the **next=state** default assignment allows designers to remove loopback transition assignments from the RTL code wherever there is a feedback loop on that state so there will be fewer RTL equations than transition arcs in the state diagram.

The RTL synthesis advantage is that making X-assignments is like putting X's into a K-Map for unused states and all digital design engineers recognize that adding X's to a K-Map allows engineers or tools to make larger groupings, enabling smaller sums-of-products, which can infer smaller combinatorial logic (at least in theory).

Making a **next=state** pre-default assignment only has one minor advantage over the **next='x** predefault assignment. Any state with a loopback transition can be omitted from the RTL code since that state will not take another transition branch and will remain in the same state; thus potentially removing a few lines of code.

Since debug time is a primary concern in RTL design, we recommend using the pre-default **next='x** assignment style.

**Checklist item:** Use the pre-default **next='x** assignment at the top of the **always\_comb** procedure.

#### 7.8 Next state naming convention

We prefer to use the identifiers state and next, not state and nextstate. There is nothing wrong

with using **nextstate** except that it is a needlessly long identifier that lengthens the code on all of the **next** assignments in the combinatorial **always\_comb** procedure.

We know that **next** is a keyword in VHDL so those with a VHDL background tend to gravitate towards using the **nextstate** identifier, but **next** is not a keyword in SystemVerilog and SystemVerilog coders can make their designs more concise by using the **next** identifier instead of using **nextstate**. As previously mentioned, we prefer concise code.

**Checklist item:** Extra points for using **next** instead of using **nextstate** in the FSM design, but both work fine.

#### 7.9 Next assignments placed in a column

Since readability and the ability to quickly identify RTL coding errors are very important, we also place all of the always\_comb next assignments neatly in a column positioned towards the right margin of the RTL code as shown in Example 8. We find it easier to scan the next assignments when they are in a neat column as opposed to next assignments that follow the contour of the code as shown in Example 9. This style also has the advantage that if an engineer ever mistakenly uses a mixture of blocking and nonblocking assignments in the next assignments, is it visually very obvious in the slightly misaligned column of next assignments.

```

always_comb begin

next = XXX;

case (state)

IDLE : if (go) next = READ;

else next = IDLE; //@ loopback

READ : next = DLY;

DLY : if (!ws) next = DONE;

else next = READ;

DONE : next = IDLE;

default: next = XXX;

endcase

end

```

Of course the simulation and synthesis of both of the above examples will be identical. The column alignment is used to quickly understand and debug the **always\_comb next** assignments.

**Checklist item:** Extra points for placing the **next** assignments in a neat column in the FSM RTL code.

#### 7.10 Loopback next state assignments

Any state in the state diagram with a loopback state must be coded into the **always\_comb** portion of the design. There are two ways to handle the loopback assignments depending on how the default **next** assignment was implemented.

If the pre-default **next='x** was used (which is what we recommend), the loopback assignment must be coded, but we recommend that the loopback be implemented as the **else** -clause of an **if-else**-**if** statement. We further recommend that a comment be added to the loopback **else**-assignment of the form //@ **loopback**. The reason for this comment-style will be explained shortly.

```

always comb begin

next='x requires loopback

next = XXX;

state assignment

case (state)

IDLE : if (go) next = READ;

Loopback state

else next = IDLE; //@ loopback

to IDLE

READ :

next = DLY;

!rst n

DLY : if (!ws) next = DONE;

go=0

else next = READ;

IDLE

DONE :

next = IDLE;

rd=0

next = XXX;

default:

ds=0

endcase

ao=1

end

always_comb begin

next=state requires NO

next = state;+

loopback state assignment

case (state)

IDLE : if (go) next = READ;

READ :

next = DLY;

DLY : if (!ws) next = DONE;

else next = READ;

DONE :

next = IDLE;

default:

next = XXX;

endcase

end

```

Figure 9 - FSM loopback state assignment styles

If the pre-default **next=state** is used, the loopback assignment can be omitted from the **if-elseif** statement since the **next** state is already assigned to stay in the current state.

The reason for using the //@ loopback comment and placing the loopback into the final else - clause is that it makes it very easy to convert from the next='x pre-default to the next=state pre-default style of always\_comb procedure (although we do not recommend the latter). The RTL coder simply replaces next='x with next=state and then deletes all lines that have the //@ loopback comment.

#### 7.11 Default output assignments

When coding the outputs in an FPGA design, we have observed that some engineers make all of the output assignments for each state of the **case** statement. We discourage this practice for the following reasons:

It is easy to miss an output assignment for one of the states, which means that the missed output

must not change for that state and that will infer a latch when synthesized.

Listing all of the outputs for each state causes the FSM RTL design code to grow in size very quickly.

Listing all of the outputs for each state makes it confusing for an engineer to determine which outputs have changed in which states. Engineers often try to examine the output assignments for the preceding and next states in an attempt to try to figure out what has changed in *this* state.

A better coding practice is to place default output assignments before the output-assignment **case** statement and then to update the appropriate outputs for each state where the outputs change as shown in Example 10.

```

always_ff @(posedge clk, negedge rst_n)

if (!rst n) begin

rd <= '0;

ds <= '0;

end

else begin

rd <= '0;

ds <= '0;

case (next)

IDLE : ;

READ : rd <= '1;

DLY : rd <= '1;

DONE : ds <= '1;

default: {rd,ds} <= 'x;</pre>

endcase

end

endmodule

```

Example 10 - FSM registered output assignments using an always\_ff procedure

This coding style offers two significant advantages over making all output assignments for each state.

First, the code becomes more concise. Second an engineer can plainly see which outputs change for each state, thus making the code more readable, easier to understand and easier to debug.

This style requires less code (one of our goals) and makes the design easier to debug (also one of our goals).

**Checklist item:** Place pre-default output assignments before the output-assignment **case** statement and then update the appropriate outputs for each state where the outputs change.

#### 7.12 Nonblocking Assignment race conditions?

The code shown in Example 10 shows default output assignments using nonblocking assignments followed by more nonblocking assignments to the same outputs in the **case** statement. We are often asked if this is a race condition in Verilog and SystemVerilog? The answer is no and the coding style shown is both proper and recommended.

The question arises due to an error in the 1995 Verilog Standard[13]. Section 5.4.1 of the 1995 Verilog Standard correctly states that two nonblocking assignments to the same variable are queued in the order that they are executed such that the last assignment wins (in more official verbiage). In the same 1995 Verilog Standard, Section 9.2.2 includes an example with a mistake where two assignments are sequentially executed and the description states that the "final value ... is indeterminate." That description was wrong.

The 2001 Verilog Standard[14] fixed the example in section 9.2.2 to have parallel execution of the two assignments, which indeed is a race condition; thus, Section 5.4.1 clearly governs the behavior of two sequentially executed nonblocking assignments and last assignment wins.

There is no race condition in Example 10.

### 8. Benchmark FSM designs

This paper examines coding efforts and Design Compiler synthesis results for four different FSM benchmark designs: FSM1, FSM7, FSM8 and Prep4. Each design includes a state diagram and a description of the RTL code using the four different FSM coding styles, 1-always block with registered outputs, 2-always block with combinatorial outputs, 3-always block with registered outputs and 4-always block with registered outputs. The full RTL code for each example is included in Appendix 2.

For benchmark purposes, we have noted the number of lines of code required to complete each of the four coding styles that incorporated the pre-default-X assignments and included all of the loopback assignments. We believe the pre-default-X with explicit loopback code to be indicative of the coding effort for each FSM design. We also assigned our evaluation for each of the original coding goals for each style as described in Section 3. We have included coding observations for the designs in each of the four FSM sections.

The synthesis results were tested using the 1-always block, 2-always block, 3-always block and 4always block coding styles. Each of these four coding styles was also tested with slight variations, specifically, each was tested **without** using **case-default**-X assignments (No case-default-X), **with case-default**-X assignments (case-default X) and then used case-default-X with pre-default-X (required "Explicit loopback" assignments) and **with next=state** (used "Implicit loopback" assignments).

To see if there have been improvements between a 2015 version and a 2018 version of Design Compiler (DC), the "No Default X" and "Default X" variations were synthesized using both versions (explicit DC versions are noted in 0), but when we saw absolutely no difference in synthesized results, we quit using the 2015 version and synthesized all of the coding variations only using the 2018 version of DC.

Synthesis compilation was done using two available ASIC libraries, the LSI 10K library, which has been included in all of the DC releases, but which is also a rather old library with limited modern capabilities. We also used an SAED32 (Synopsys Armenia Educational Department 32nm) library that is included with a Synopsys BitCoin online example.

Default synthesis was done without any clocking goals and using abstract enumerated types (no assigned state encodings). Then a create\_clock clk-period 0 was executed after compiling the design and before doing report\_area and report\_timing to show the default delay (negative slack) through each design. Note that abstract enumerated types are assigned integer values by SystemVerilog starting with the first state listed equal to zero and each successive state incrementing by 1. These in-order binary counts are typically not very efficient when synthesized.

Based on the default delays, a **create\_clock** command was issued with a realistic clock period plus all inputs were given 80% of the clock style while all outputs were given 20% of the clock cycle.

The second iteration of each design used semi-intelligent binary encoded values assigned to each state and some effort was made to choose encodings that would give Gray-like transitions as much as possible. Then the designs were again synthesized, first with no clock goal and then with clock input and output design constraints.

None of the designs up to this point used **case-default** values set to all X's ( **case-default**-X). In the tables for each FSM design, these are referred to as the "No case-default-X" values.

Since adding default X's to a **case** statement is similar adding X's to a K-Map, default X-values were assigned to next states and outputs in the **case** statements and the previous synthesis exercises were repeated. These are referred to as the "Default X" values in the tables.

The next synthesis iteration was to change the **next** = **'x** assignments to **next** = **state** and to remove all of the loopback code from the **case** statements. The theory being tested is that synthesis might improve if the state does not transition and if the extra code is removed from each design. Then the synthesis runs were executed again. These are referred to as the "Default X - No Loopback" values in the tables.

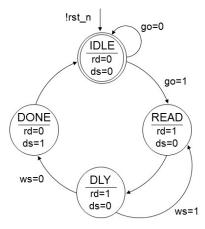

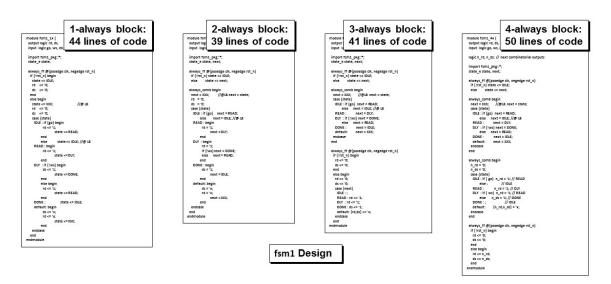

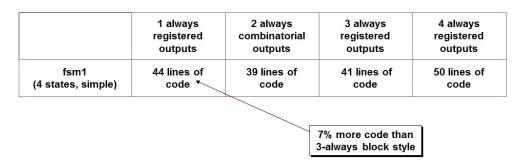

### 8.1 FSM1 with 4 states, 2 outputs and 2 inputs

The FSM1 design, shown in Figure 10, has an asynchronous low-true **rst\_n**, two inputs **go** and **ws** (wait state), and two outputs **rd** (read) and **ds** (done strobe).

Figure 10 - FSM1 state diagram

There is one loopback state in the FSM1 design and that is in the **IDLE** state.

The coding effort for small FSM designs using the different styles does not differ significantly, but it will differ dramatically as the number of states and outputs increases.

Figure 11 - fsm1 - Coding styles effort comparison

Figure 11 shows the relative coding difference between the four coding styles. The full fsm1 RTL code for all four coding styles used in Figure 11 are shown in Appendix 2.2 - Appendix 2.5. The **fsm1\_pkg** files with both abstract and binary encoded **typedef**[s] that were used by all of the fsm1 designs are shown in Appendix 2.1.

|        |          | Design ( | Compile  | r <b>O-201</b> 8 | .06-SP4    |          | LSI 10K | _SI 10K Library - lsk_10k |           |           |          |      |          |           |                |        |

|--------|----------|----------|----------|------------------|------------|----------|---------|---------------------------|-----------|-----------|----------|------|----------|-----------|----------------|--------|

|        |          | No cas   | se-defau | lt-X / Ex        | plicit loo | pback    | case    | -default                  | -X / Expl | icit loop | back     | case | -default | -X / Impl | icit loop      | back   |

|        |          | RTL      | No Clo   | ck Goal          | Clock G    | ioal 7.5 | RTL     | No Clo                    | ck Goal   | Clock G   | ioal 7.5 | RTL  | No Clo   | ck Goal   | Clock Goal 7.5 |        |

|        | Enums    | LOC*     | Area     | Slack            | Area       | Slack    | LOC*    | Area                      | Slack     | Area      | Slack    | LOC* | Area     | Slack     | Area           | Slack  |

| fsm1_1 | Abstract | 39       | 52       | -5.57            | 52         | 0.04     | 44      | 50                        | -5.19     | 49        | 0.04     | 42   | 50       | -5.36     | 51             | 0.04   |

| fsm1_2 | Abstract | 34       | 32       | -4.89            | 38         | (1.68)   | 39      | 31                        | -4.94     | 35        | (1.37)   | 38   | 28       | -5.18     | 35             | (1.37) |

| fsm1_3 | Abstract | 38       | 49       | -6.37            | 49         | 0.03     | 41      | 49                        | -6.37     | 49        | 0.03     | 40   | 49       | -6.37     | 57             | 0.04   |

| fsm1_4 | Abstract | 48       | 52       | -5.57            | 52         | 0.04     | 50      | 52                        | -5.57     | 52        | 0.04     | 49   | 53       | -5.10     | 52             | 0.04   |

|        |          |          |          |                  |            |          |         |                           |           |           |          |      |          |           |                |        |

| fsm1_1 | Encoded  | 39       | 44       | -4.08            | 44         | 0.04     | 44      | 44                        | -4.08     | 44        | 0.04     | 42   | 44       | -4.08     | 44             | 0.04   |

| fsm1_2 | Encoded  | 34       | 26       | -4.09            | 28         | (1.16)   | 39      | 26                        | -4.09     | 28        | (1.16)   | 38   | 26       | -4.09     | 27             | (1.16) |

| fsm1_3 | Encoded  | 38       | 44       | -5.06            | 45         | 0.04     | 41      | 44                        | -5.06     | 45        | 0.04     | 40   | 44       | -5.06     | 45             | 0.04   |

| fsm1_4 | Encoded  | 48       | 44       | -4.08            | 44         | 0.04     | 50      | 44                        | -4.08     | 44        | 0.04     | 49   | 44       | -4.08     | 44             | 0.04   |

|        |          |          |          |                  |            |          |         |                           |           |           |          |      |          |           |                |        |

LOC\* - Lines Of Code (not including imported enums)

|        |          | Design ( | Compilei | r O-2018  | .06-SP4    |          | SAED Library - saed32rvt_ss0p95v125c.db |          |           |           |          |                                    |        |         |         |          |

|--------|----------|----------|----------|-----------|------------|----------|-----------------------------------------|----------|-----------|-----------|----------|------------------------------------|--------|---------|---------|----------|

|        |          | No ca    | se-defau | lt-X / Ex | plicit loo | pback    | case                                    | -default | -X / Expl | icit loop | back     | case-default-X / Implicit loopback |        |         |         |          |

|        |          | RTL      | No Clo   | ck Goal   | Clock G    | oal 0.65 | RTL                                     | No Clo   | ck Goal   | Clock G   | oal 0.65 | RTL                                | No Clo | ck Goal | Clock G | oal 0.65 |

|        | Abstract | LOC*     | Area     | Slack     | Area       | Slack    | LOC*                                    | Area     | Slack     | Area      | Slack    | LOC*                               | Area   | Slack   | Area    | Slack    |

| fsm1_1 | Abstract | 39       | 51       | -0.42     | 54         | 0.00     | 44                                      | 51       | -0.40     | 52        | 0.00     | 42                                 | 52     | -0.39   | 54      | 0.00     |

| fsm1_2 | Abstract | 34       | 34       | -0.38     | 54         | (0.12)   | 39                                      | 34       | -0.40     | 42        | (0.09)   | 38                                 | 32     | -0.40   | 43      | (0.09)   |

| fsm1_3 | Abstract | 38       | 48       | -0.50     | 49         | 0.00     | 41                                      | 48       | -0.50     | 49        | 0.00     | 40                                 | 48     | -0.50   | 48      | 0.00     |

| fsm1_4 | Abstract | 48       | 51       | -0.42     | 54         | 0.00     | 50                                      | 51       | -0.42     | 54        | 0.00     | 49                                 | 50     | -0.40   | 52      | 0.00     |

|        |          |          |          |           |            |          |                                         |          |           |           |          |                                    |        |         |         |          |

| fsm1_1 | Encoded  | 39       | 42       | -0.38     | 44         | 0.00     | 44                                      | 42       | -0.38     | 44        | 0.00     | 42                                 | 42     | -0.37   | 44      | 0.00     |

| fsm1_2 | Encoded  | 34       | 26       | -0.35     | 31         | (0.06)   | 39                                      | 26       | -0.35     | 31        | (0.06)   | 38                                 | 26     | -0.35   | 29      | (0.06)   |